## NIST Internal Report NIST IR 8517 ipd

# **Hardware Security Failure Scenarios**

Potential Weaknesses in Hardware Design

**Initial Public Draft**

Peter Mell Irena Bojanova

This publication is available free of charge from: https://doi.org/10.6028/NIST.IR.8517.ipd

## NIST Internal Report NIST IR 8517 ipd

# **Hardware Security Failure Scenarios**

Potential Weaknesses in Hardware Design

**Initial Public Draft**

Peter Mell Computer Security Division Information Technology Laboratory

Irena Bojanova Software and Systems Division Information Technology Laboratory

This publication is available free of charge from: https://doi.org/10.6028/NIST.IR.8517.ipd

June 2024

U.S. Department of Commerce *Gina M. Raimondo, Secretary*

National Institute of Standards and Technology Laurie E. Locascio, NIST Director and Under Secretary of Commerce for Standards and Technology Certain equipment, instruments, software, or materials, commercial or non-commercial, are identified in this paper in order to specify the experimental procedure adequately. Such identification does not imply recommendation or endorsement of any product or service by NIST, nor does it imply that the materials or equipment identified are necessarily the best available for the purpose.

There may be references in this publication to other publications currently under development by NIST in accordance with its assigned statutory responsibilities. The information in this publication, including concepts and methodologies, may be used by federal agencies even before the completion of such companion publications. Thus, until each publication is completed, current requirements, guidelines, and procedures, where they exist, remain operative. For planning and transition purposes, federal agencies may wish to closely follow the development of these new publications by NIST.

Organizations are encouraged to review all draft publications during public comment periods and provide feedback to NIST. Many NIST cybersecurity publications, other than the ones noted above, are available at <a href="https://csrc.nist.gov/publications">https://csrc.nist.gov/publications</a>.

#### **NIST Technical Series Policies**

Copyright, Use, and Licensing Statements NIST Technical Series Publication Identifier Syntax

#### **Publication History**

Approved by the NIST Editorial Review Board on YYYY-MM-DD [will be added in final publication]

#### How to Cite this NIST Technical Series Publication

Mell P, Bojanova I (2024) Hardware Security Failure Scenarios: Potential Weaknesses in Hardware Design. (National Institute of Standards and Technology, Gaithersburg, MD), NIST Interagency or Internal Report (IR) NIST IR 8517 ipd. https://doi.org/10.6028/NIST.IR.8517.ipd

#### Author ORCID iDs

Peter Mell: 0000-0003-2938-897X Irena Bojanova: 0000-0002-3198-7026

#### **Contact Information**

nistir8517@nist.gov

National Institute of Standards and Technology Attn: Computer Security Division, Information Technology Laboratory 100 Bureau Drive (Mail Stop 8930) Gaithersburg, MD 20899-8930

#### Public Comment Period

June 13, 2024 – July 31, 2024

#### Submit Comments

nistir8517@nist.gov

National Institute of Standards and Technology Attn: Computer Security Division, Information Technology Laboratory 100 Bureau Drive (Mail Stop 8930) Gaithersburg, MD 20899-8930

#### Additional Information

Additional information about this publication is available at <u>https://csrc.nist.gov/pubs/ir/8517/ipd</u>, including related content, potential updates, and document history.

All comments are subject to release under the Freedom of Information Act (FOIA).

#### 1 Abstract

- 2 Historically, hardware has been assumed to be inherently secure. However, chips are both

- 3 created with and contain complex software, and software is known to have bugs. Some of these

- 4 bugs will compromise security. This publication evaluates the types of vulnerabilities that can

- 5 occur, leveraging existing work on hardware weaknesses. For each type, a security failure

- 6 scenario is provided that describes **how** the weakness could be exploited, **where** the weakness

- 7 typically occurs, and **what** kind of damage could be done by an attacker. The 98 failure

- 8 scenarios provided demonstrate the extensive and broadly distributed possibilities for

- 9 hardware-related security failures.

#### 10 Keywords

11 chips; design; failures; hardware; scenarios; security; vulnerability; weakness.

## 12 Reports on Computer Systems Technology

- 13 The Information Technology Laboratory (ITL) at the National Institute of Standards and

- 14 Technology (NIST) promotes the U.S. economy and public welfare by providing technical

- 15 leadership for the Nation's measurement and standards infrastructure. ITL develops tests, test

- 16 methods, reference data, proof of concept implementations, and technical analyses to advance

- 17 the development and productive use of information technology. ITL's responsibilities include

- 18 the development of management, administrative, technical, and physical standards and

- 19 guidelines for the cost-effective security and privacy of other than national security-related

- 20 information in federal information systems.

## 21 Audience

- 22 This report is intended for a broad audience who wants to understand the many ways in which

- 23 hardware can fail from a security perspective. This includes policymakers interested in

- 24 information technology (IT) security, IT security officers, operation security staff who must

- 25 secure deployed hardware, and developers of hardware. It is written for a technically oriented

- 26 audience, but it does not require specific knowledge of hardware security.

- 27

#### 28 Call for Patent Claims

- 29 This public review includes a call for information on essential patent claims (claims whose use

- 30 would be required for compliance with the guidance or requirements in this Information

- 31 Technology Laboratory (ITL) draft publication). Such guidance and/or requirements may be

- 32 directly stated in this ITL Publication or by reference to another publication. This call also

- includes disclosure, where known, of the existence of pending U.S. or foreign patent

- 34 applications relating to this ITL draft publication and of any relevant unexpired U.S. or foreign

- 35 patents.

- 36 ITL may require from the patent holder, or a party authorized to make assurances on its behalf,37 in written or electronic form, either:

- a) assurance in the form of a general disclaimer to the effect that such party does not hold

and does not currently intend holding any essential patent claim(s); or

- b) assurance that a license to such essential patent claim(s) will be made available to

applicants desiring to utilize the license for the purpose of complying with the guidance

or requirements in this ITL draft publication either:

- 43 i. under reasonable terms and conditions that are demonstrably free of any unfair44 discrimination; or

- 45 ii. without compensation and under reasonable terms and conditions that are46 demonstrably free of any unfair discrimination.

- 47 Such assurance shall indicate that the patent holder (or third party authorized to make

- 48 assurances on its behalf) will include in any documents transferring ownership of patents

- 49 subject to the assurance, provisions sufficient to ensure that the commitments in the assurance

- 50 are binding on the transferee, and that the transferee will similarly include appropriate

- 51 provisions in the event of future transfers with the goal of binding each successor-in-interest.

- 52 The assurance shall also indicate that it is intended to be binding on successors-in-interest

- regardless of whether such provisions are included in the relevant transfer documents.

- 54 Such statements should be addressed to: <u>nistir8517@nist.gov</u>.

## 55 Table of Contents

| 56 | 1. Introduction1                                             |

|----|--------------------------------------------------------------|

| 57 | 2. Background2                                               |

| 58 | 2.1. Weaknesses vs. Vulnerabilities2                         |

| 59 | 2.2. Weakness Data Fields2                                   |

| 60 | 2.3. Weakness Abstractions                                   |

| 61 | 2.4. Weakness Views3                                         |

| 62 | 2.4.1. Hardware Design View                                  |

| 63 | 2.4.2. Research Concepts View4                               |

| 64 | 2.4.3. Simplified Mapping of Published Vulnerabilities View4 |

| 65 | 3. Technical Approach6                                       |

| 66 | 3.1. Concept of Hardware Security Failure Scenarios6         |

| 67 | 3.1.1. Determining How Weaknesses Occur6                     |

| 68 | 3.1.2. Determining Where Weaknesses Occur6                   |

| 69 | 3.1.3. Determining What Damage Weaknesses Allow6             |

| 70 | 3.2. Creating Hardware Weakness Subgraphs6                   |

| 71 | 4. Hardware Security Failure Scenarios9                      |

| 72 | 4.1. Improper Access Control9                                |

| 73 | 4.2. Improper Adherence to Coding Standards14                |

| 74 | 4.3. Improper Check or Handling of Exceptional Conditions16  |

| 75 | 4.4. Improper Control of a Resource Through its Lifetime18   |

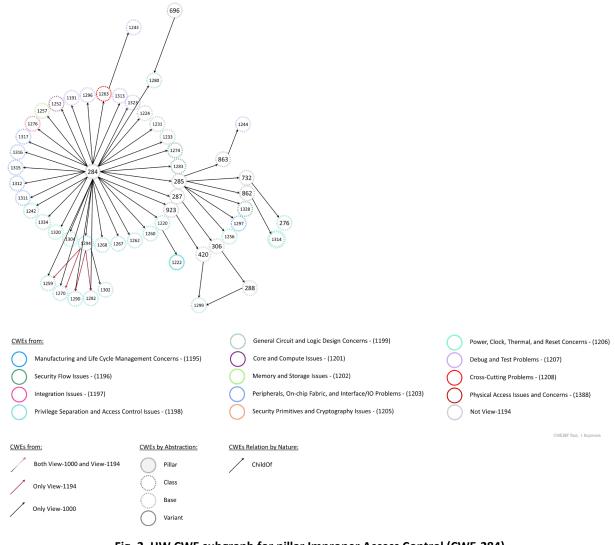

| 76 | 4.5. Incorrect Comparison22                                  |

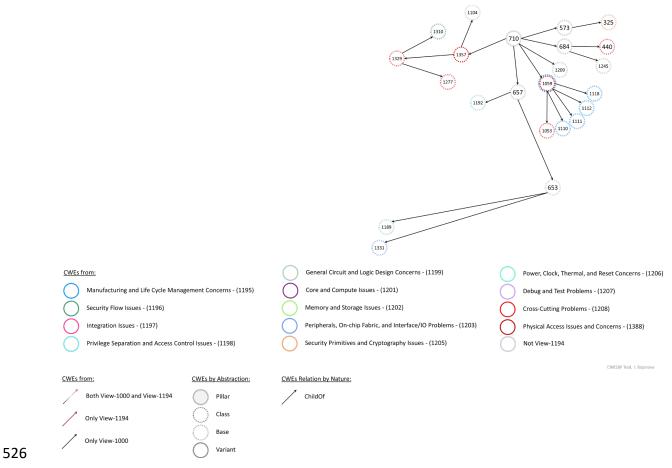

| 77 | 4.6. Insufficient Control Flow Management23                  |

| 78 | 4.7. Protection Mechanism Failure25                          |

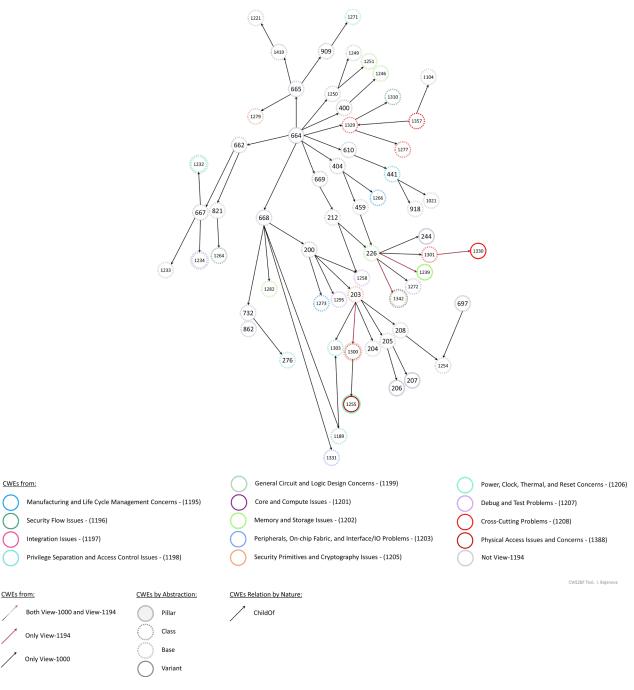

| 79 | 5. Categories of Hardware Design Weaknesses28                |

| 80 | 5.1. Core and Compute Issues                                 |

| 81 | 5.2. Cross-Cutting Problems                                  |

| 82 | 5.3. Debug and Test Problems                                 |

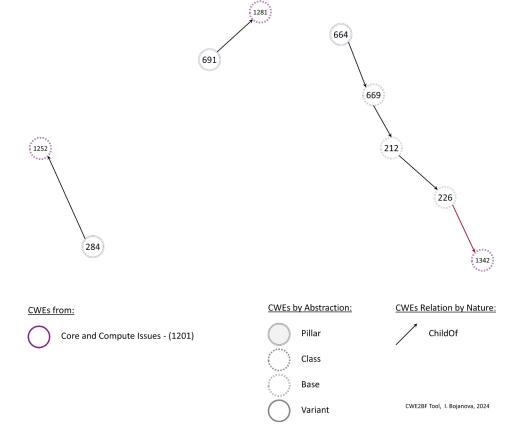

| 83 | 5.4. General Circuit and Logic Design Concerns               |

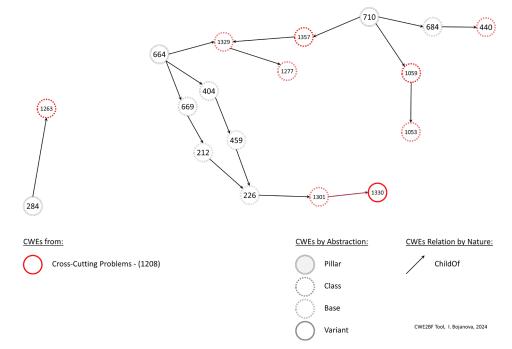

| 84 | 5.5. Integration Issues                                      |

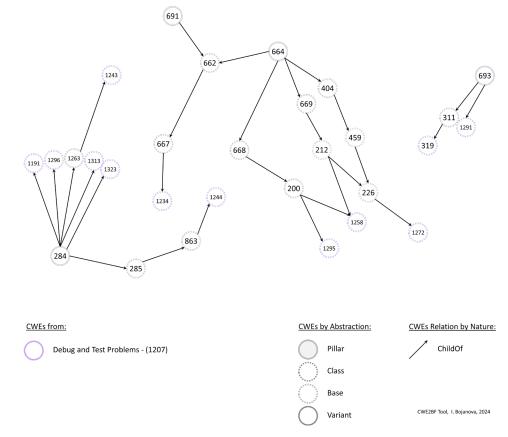

| 85 | 5.6. Manufacturing and Life Cycle Management Concerns        |

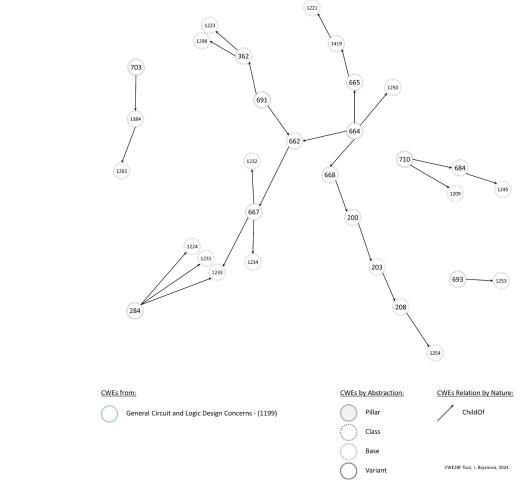

| 86 | 5.7. Memory and Storage Issues                               |

| 87 | 5.8. Peripherals, On-chip Fabric, and Interface/IO Problems  |

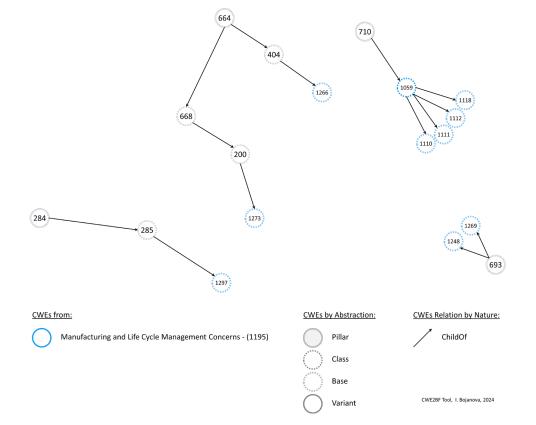

| 88 | 5.9. Physical Access Issues and Concerns                     |

| 89 | 5.10. Power, Clock, Thermal, and Reset Concerns              |

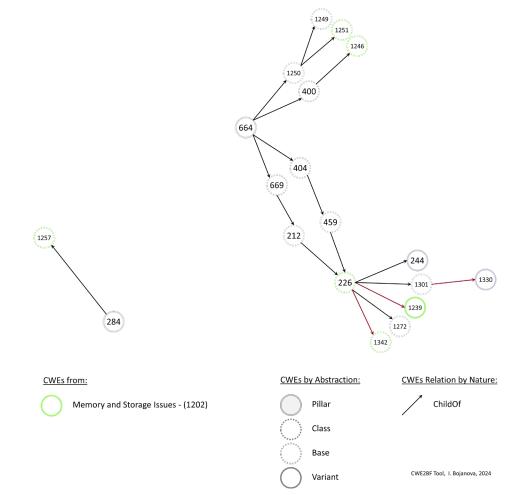

| 90  | 5.11. Privilege Separation and Access Control Issues                                   |

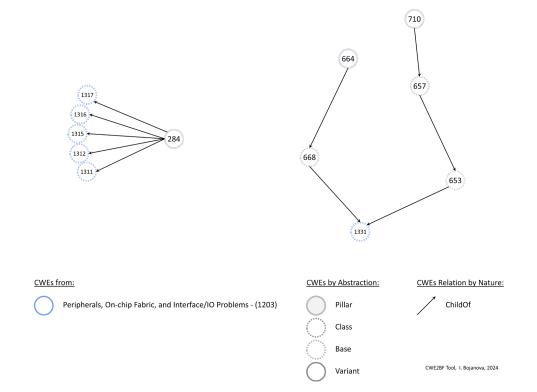

|-----|----------------------------------------------------------------------------------------|

| 91  | 5.12. Security Flow Issues                                                             |

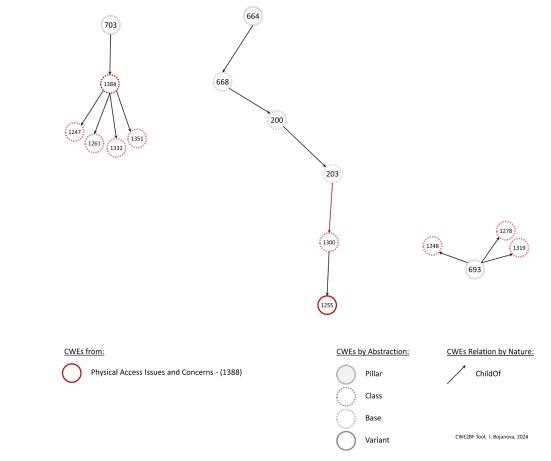

| 92  | 5.13. Security Primitives and Cryptography Issues                                      |

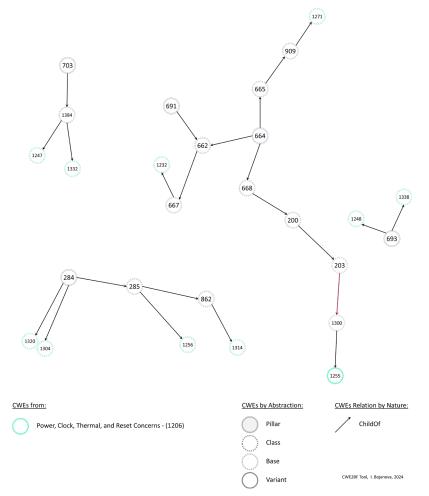

| 93  | 6. Comparison With Software Weaknesses41                                               |

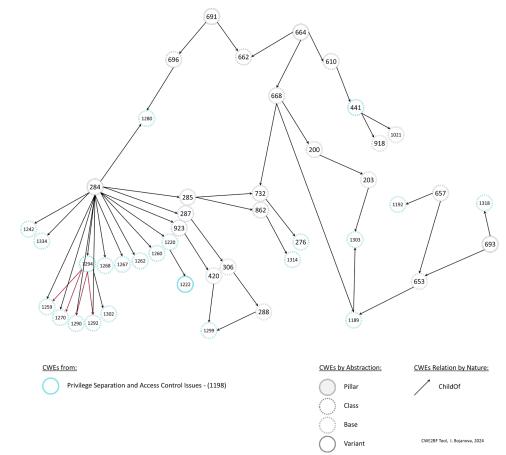

| 94  | 7. Software Assurance Trends Categories45                                              |

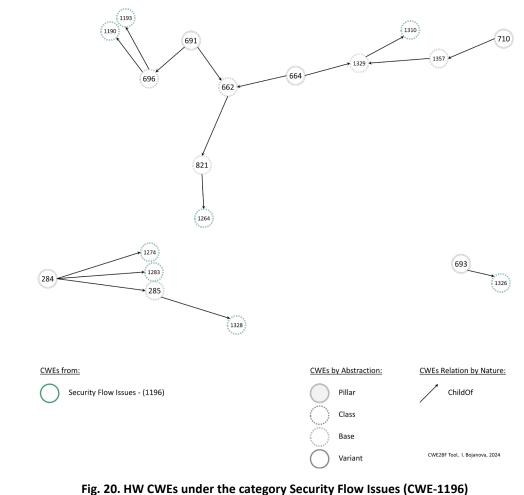

| 95  | 8. Conclusion                                                                          |

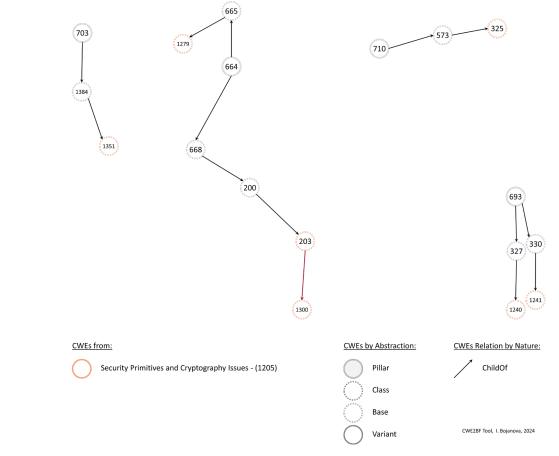

| 96  | References49                                                                           |

| 97  | Appendix A. List of Symbols, Abbreviations, and Acronyms60                             |

| 98  | Appendix B. Analysis of the Complete Hardware Weakness Graph61                         |

| 99  | B.1. Hardware Design Category Overlay61                                                |

| 100 | B.2. Comparison of View-1000 and View-1194 Relationships62                             |

| 101 | Appendix C. Weakness Hierarchy — Improper Access Control64                             |

| 102 | Appendix D. Weakness Hierarchy — Improper Adherence to Coding Standards                |

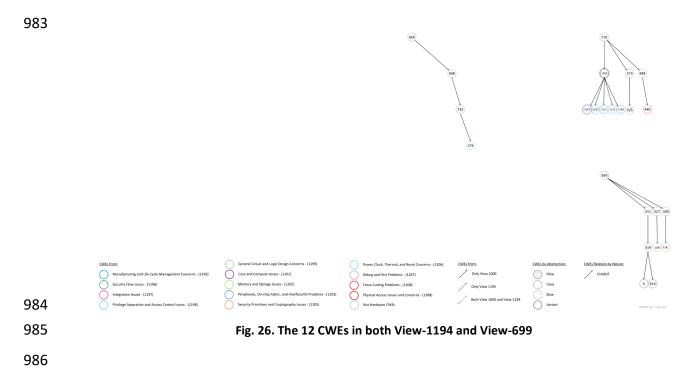

| 103 | Appendix E. Weakness Hierarchy — Improper Check or Handling of Exceptional Conditions  |

| 104 | Appendix F. Weakness Hierarchy — Improper Control of a Resource Through its Lifetime70 |

| 105 | Appendix G. Weakness Hierarchy — Incorrect Comparison73                                |

| 106 | Appendix H. Weakness Hierarchy — Insufficient Control Flow Management                  |

| 107 | Appendix I. Weakness Hierarchy — Protection Mechanism Failure                          |

## 108 List of Figures

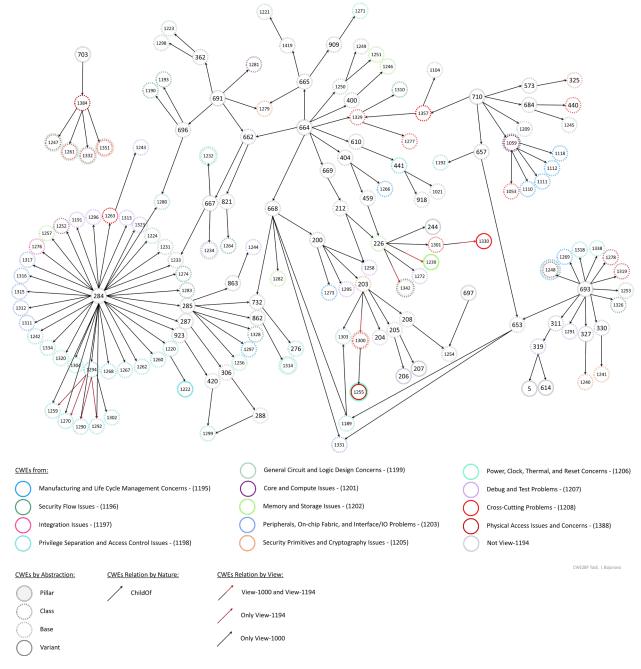

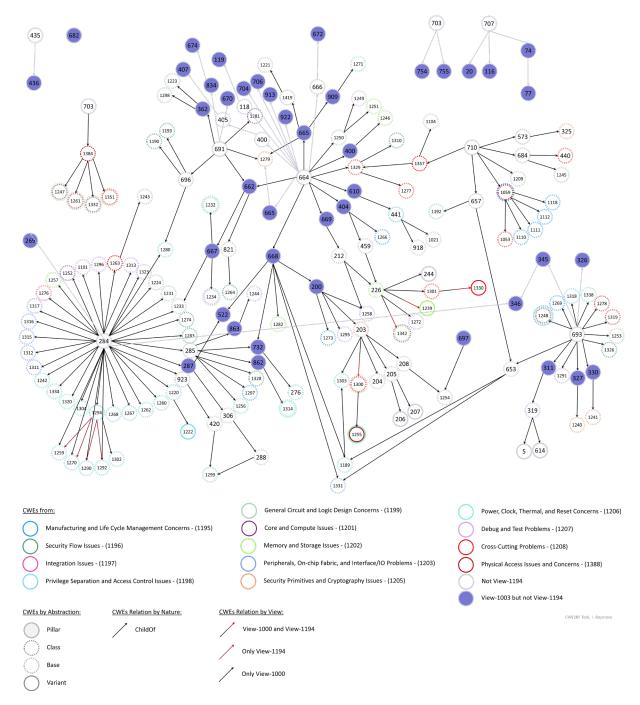

| 109        | Fig. 1. Complete HW CWE graph created using View 1000 and View 11947                                  |

|------------|-------------------------------------------------------------------------------------------------------|

| 110        | Fig. 2. HW CWE subgraph for pillar Improper Access Control (CWE-284)10                                |

| 111        | Fig. 3. HW CWE subgraph for pillar Improper Adherence to Coding Standards (CWE-710)15                 |

| 112        | Fig. 4. HW CWE subgraph for pillar Improper Adherence to Coding Standards (CWE-703)17                 |

| 113        | Fig. 5. HW CWE subgraph for pillar Improper Control of a Resource Through its Lifetime (CWE-664)19    |

| 114        | Fig. 6. HW CWE subgraph for pillar Incorrect Comparison (CWE-697)23                                   |

| 115        | Fig. 7. HW CWE subgraph for pillar Insufficient Control Flow Management (CWE-691)24                   |

| 116        | Fig. 8. HW CWE subgraph for pillar Protection Mechanism Failure (CWE-693)26                           |

| 117        | Fig. 9. HW CWEs under the category Core and Compute Issues (CWE-1201)28                               |

| 118        | Fig. 10. HW CWEs under the category Cross-Cutting Problems (CWE-1208)29                               |

| 119        | Fig. 11. HW CWEs under the category Debug and Test Problems (CWE-1207)30                              |

| 120        | Fig. 12. HW CWEs under the category General Circuit and Logic Design Concerns (CWE-1199)31            |

| 121        | Fig. 13. HW CWEs under the category Integration Issues (CWE-1197)32                                   |

| 122<br>123 | Fig. 14. HW CWEs under the category Manufacturing and Life Cycle Management Concerns (CWE-<br>1195)33 |

| 124        | Fig. 15. HW CWEs under the category Memory and Storage Issues (CWE-1202)                                       |

|------------|----------------------------------------------------------------------------------------------------------------|

| 125<br>126 | Fig. 16. HW CWEs under the category Peripherals, On-chip Fabric, and Interface/IO Problems (CWE-<br>1203)      |

| 127        | Fig. 17. Figure 18. HW CWEs under the category Physical Access Issues and Concerns (CWE-1388)36                |

| 128        | Fig. 18. HW CWEs under the category Power, Clock, Thermal, and Reset Concerns (CWE-1206)37                     |

| 129        | Fig. 19. HW CWEs under the category Privilege Separation and Access Control Issues (CWE-1198)38                |

| 130        | Fig. 20. HW CWEs under the category Security Flow Issues (CWE-1196)                                            |

| 131        | Fig. 21. HW CWEs under the category Security Primitives and Cryptography Issues (CWE-1205)40                   |

| 132<br>133 | Fig. 22. HW CWE complete graph with View-1003 pillar and class CWEs that are not in View-1194<br>highlighted42 |

| 134<br>135 | Fig. 23. HW CWE complete graph with View-1003 base CWEs that overlap with View-1194 highlighted<br>43          |

| 136        | Fig. 24. HW CWE complete graph with memory-related weaknesses highlighted                                      |

| 137        | Fig. 25. View-699 CWEs that overlap with View-1194 highlighted45                                               |

| 138        | Fig. 26. The 12 CWEs in both View-1194 and View-69947                                                          |

| 139        | Fig. 27. HW CWE Category Graph: Improper Access Control65                                                      |

| 140        |                                                                                                                |

#### 141 **1. Introduction**

- 142 Historically, hardware has been viewed as "an immutable root-of-trust" with no security issues

- 143 [1]. It has been assumed to be inherently secure. However, chips are created with and contain

- 144 complex software, and software is known to have bugs. It is not unusual to have 1-25 bugs per

- 145 1000 lines of code for delivered software [2], and some of these bugs will have security

- 146 implications. Further complicating matters, many of these bugs are hard-coded onto silicon,

- 147 which can make mitigation challenging.

- 148 This work describes and categorizes ways in which computer hardware (HW) (i.e., chips) can fail

- 149 from a security perspective. It does this by enumerating 98 scenarios that represent potential

- 150 weaknesses in the programming and physical aspects of HW design. The purpose is to highlight

- 151 the dangers of vulnerabilities potentially being introduced into the HW design process.

- 152 The Common Weakness Enumeration (CWE) [8][9] is a list of weaknesses. In this context, a

- 153 weakness is defined as "a condition in a software, firmware, hardware, or service component

- that, under certain circumstances, could contribute to the introduction of vulnerabilities" [4].

- 155 CWE designators of the form (CWE-XXXX) are given to each of the 934 listed weaknesses (as of

- 156 January 26, 2024). Each weakness entry contains complex, multi-page data elements with

- detailed security information. Since the inception of CWEs, a primary focus has been software

- 158 weaknesses, while coverage of hardware-specific weaknesses has been more recent. All CWEs

- 159 can be viewed by using the 'ID Lookup' search box on the CWE webpage [9].

- As of April 29, 2024, the HW CWE Special Interest Group (HW CWE SIG) [5] has curated a list of

- 161 108 HW CWEs focused on HW design issues. The list includes a few CWEs that were created for

- 162 software weaknesses but that are also relevant to HW weaknesses. These 'software' CWEs have

- 163 been expanded to include HW-specific details and examples. However, the majority of the

- 164 CWEs on the list are HW-specific and do not apply to the software domain. This indicates that

- 165 HW security is fundamentally different from software security, despite the fact that both are

- 166 created with and contain code. This publication demonstrates the uniqueness of HW security

- and the very different challenges presented compared to software security. At the same time,

HW can contain weaknesses commonly found in software, and an HW weakness may be linked

- 169 in a chain of weaknesses that include software weaknesses.

- 170 The HW security failure scenarios in this publication are based on the HW CWEs. For the

- 171 purposes of this publication, an HW security failure scenario briefly describes how an attacker

- can cause a particular type of damage where the exploit typically occurs. Focusing on

- 173 weaknesses enables one to look at the set of potential dangers, inclusive of and beyond the set

- 174 of publicly published vulnerabilities. While reasonably comprehensive, the failure scenarios are

- not intended to provide exhaustive coverage. Their purpose is to highlight the significant

- 176 danger presented by each HW weakness.

177

#### 178 2. Background

- 179 This section provides the background for understanding the technical approach and

- 180 categorization system used in creating and organizing the HW security failure scenarios.

- 181 Readers interested in simply perusing the failure scenarios without understanding how they

- 182 were derived or organized should go directly to Sec. 4.

#### 183 **2.1. Weaknesses vs. Vulnerabilities**

- 184 A weakness can also be defined as a bug or fault type that can be exploited through an

- 185 operation that results in a security-relevant error [3]. The word 'type' is critical as it conveys

- 186 that a weakness is a concept that can be instantiated in software or hardware; a weakness is

- 187 not specific to a particular program or chip. A vulnerability, however, is tied to a specific piece

- 188 of code or chip. A vulnerability is an instantiation of a weakness. Complicating matters, some

- 189 vulnerabilities arise only in the context of a chain of weaknesses [3].

- 190 Vulnerabilities are enumerated in the Common Vulnerabilities and Exposures (CVE) list [6]. The

- 191 National Vulnerability Database contains details on each CVE [7]. There are over 25,000 CVEs

- 192 published annually, with the rate usually growing each year. As of February 22, 2024 only 131

- 193 of these are HW CVEs.

## 194 2.2. Weakness Data Fields

- Every weakness in the CWE is described by a set of elements. The following are the CWE datafields leveraged in the creation of the HW failure scenarios:

- 197 1. **Description/Extended Description** Detailed explanation of the fault type

- Relationships/Memberships Taxonomic information to organize weaknesses into

hierarchies and categories

- 3. Modes of Introduction Descriptions of the life cycle phase where the CWE can be

introduced

- 202 4. Applicable Platforms Involved languages and technologies

- 203 5. Common Consequences Affected security attributes along with likelihoods (e.g.,

204 confidentiality, integrity, availability, access control, authentication, and authorization)

- 205 6. **Demonstrative Examples** Hypothetical examples of the weakness

- 206 7. Observed Examples Actual observed examples of the weakness, usually with CVE

207 references

- 208 8. **Potential Mitigations** Protection methods

#### 209 **2.3. Weakness Abstractions**

- 210 The CWE weaknesses model is composed of four layers of abstraction: pillar (P), class (C), base

- 211 (B), and variant (V)<sup>1</sup>. The abstraction reflects the extent to which issues are being described in

- terms of five dimensions: behavior, property, technology, language, and resource. Variant

- 213 weaknesses are at the most specific level of abstraction and describe at least three dimensions.

- Base weaknesses are more abstract than variants and more specific than classes; they describe

- 215 two to three dimensions. Class weaknesses are very abstract and not typically specific about

- any language or technology; they describe one to two dimensions. Pillar weaknesses are at the

- 217 highest level of abstraction. In this work, pillars and classes are used to organize the HW

- 218 security failure scenarios.

#### 219 2.4. Weakness Views

- 220 CWE designators of the form (CWE-XXXX) are given to weaknesses, views, and categories. A

- view provides a hierarchical organization of CWEs from a particular perspective (e.g., software

- development, research, and hardware design). A category is a simpler construct that groups a

- set of CWEs that have some similarity. Views may contain categories within their hierarchy.

- As of February 9, 2024, the CWE contains 49 views and 374 categories. There are three views

- 225 pertinent to this work: Hardware Design view (<u>CWE-1194</u>), Research Concepts view (<u>CWE-</u>

- 226 <u>1000</u>), and the Weaknesses for Simplified Mapping of Published Vulnerabilities view (<u>CWE-</u>

- 227 <u>1003</u>).

## 228 2.4.1. Hardware Design View

- 229 The Hardware Design view (<u>CWE-1194</u>) organizes the 108 HW weakness CWEs using 13

- 230 categories. This view is a three-level hierarchy with CWE-1194 as its root, the 13 categories<sup>2</sup> as

- children of the root, and a tree of HW weakness CWEs under each category. HW weaknesses

- 232 may occur under multiple categories, although most do not.

- 233 The 13 categories of HW design weaknesses are:

- 1. Core and Compute Issues (<u>CWE-1201</u>)

- 235 2. Cross-Cutting Problems (<u>CWE-1208</u>)

- 236 3. Debug and Test Problems (<u>CWE-1207</u>)

- 237 4. General Circuit and Logic Design Concerns (<u>CWE-1199</u>)

- 238 5. Integration Issues (<u>CWE-1197</u>)

- 239 6. Manufacturing and Life Cycle Management Concerns (<u>CWE-1195</u>)

- 240 7. Memory and Storage Issues (<u>CWE-1202</u>)

<sup>&</sup>lt;sup>1</sup> A compound element (linking together weaknesses) associates two or more interacting or co-occurring CWEs. None of the HW CWEs are of the compound abstraction.

<sup>&</sup>lt;sup>2</sup> Section 5 provides details on the 13 categories.

- 241 8. Peripherals, On-chip Fabric, and Interface/IO Problems (<u>CWE-1203</u>)

- 242 9. Physical Access Issues and Concerns (<u>CWE-1388</u>)

- 243 10. Power, Clock, Thermal, and Reset Concerns (CWE-1206)

- 244 11. Privilege Separation and Access Control Issues (<u>CWE-1198</u>)

- 245 12. Security Flow Issues (CWE-1196)

- 246 13. Security Primitives and Cryptography Issues (<u>CWE-1205</u>)

#### 247 2.4.2. Research Concepts View

- 248 The Research Concepts view (<u>CWE-1000</u>) organizes all weakness CWEs by the method through

- 249 which an exploitation can occur. It is a directed acyclic graph with a single source node, <u>CWE-</u>

- 250 <u>1000</u>. In this hierarchy, some CWEs can have multiple parents, and all of them have <u>CWE-1000</u>

as their oldest ancestor. These properties allow a CWE (even one with only one parent) to

- 252 possibly be reached through multiple paths from the root.

- 253 The children of <u>CWE-1000</u> are 10 pillars that organize the weakness CWEs. The pillar CWEs

254 marked with \* contain HW CWEs. However, none of these pillars are hardware-specific and 255 cover many software security weaknesses as well.

- 256 1. Improper Access Control (<u>CWE-284</u>) \*

- 257 2. Improper Adherence to Coding Standards (<u>CWE-710</u>) \*

- 258 3. Improper Check or Handling of Exceptional Conditions (<u>CWE-703</u>) \*

- 4. Improper Control of a Resource Through its Lifetime (<u>CWE-664</u>) \*

- 260 5. Improper Interaction Between Multiple Correctly-Behaving Entities (<u>CWE-435</u>)

- 261 6. Improper Neutralization (<u>CWE-707</u>)

- 262 7. Incorrect Calculation (<u>CWE-682</u>)

- 263 8. Incorrect Comparison (<u>CWE-697</u>)\*

- 264 9. Insufficient Control Flow Management (<u>CWE-691</u>) \*

- 265 10. Protection Mechanism Failure (<u>CWE-693</u>) \*

## 266 **2.4.3. Simplified Mapping of Published Vulnerabilities View**

- 267 The Weaknesses for Simplified Mapping of Published Vulnerabilities view (<u>CWE-1003</u>) organizes

- the weaknesses that are most commonly seen in software CVEs to assist organizations that deal

- with such data (e.g., vulnerability databases and security tool vendors).

- 270 It is a three-level tree with <u>CWE-1003</u> as its root (i.e., there is only one path to each CWE, and

- all CWEs have exactly one parent). It has no categories and organizes the CWEs by pillars and

- classes. The children of the root are 35 classes and two pillars. It contains a total of 130

NIST IR 8517 ipd (Initial Public Draft) June 2024

- 273 weaknesses, and only three of these weaknesses are also HW CWEs (<u>CWE-203</u>, <u>CWE-276</u>, and

- 274 <u>CWE-319</u>).

#### 275 **3. Technical Approach**

- 276 This section describes the concept of a hardware security failure scenario and the approach to

- 277 creating weakness graphs to organize them.

## 278 **3.1. Concept of Hardware Security Failure Scenarios**

- 279 For the purposes of this work, a hardware security failure scenario describes a malicious entity

- 280 (e.g., human attacker or automated malware) leveraging a weakness to violate security policy.

- 281 Each failure scenario has three aspects: **how** the weakness could be exploited, **where** the

- weakness typically occurs, and **what** kind of damage could be done.

- 283 While reasonably comprehensive, the failure scenarios are not intended to provide exhaustive

- 284 coverage. Their purpose is to highlight the dangers presented by each HW weakness.

## 285 **3.1.1. Determining How Weaknesses Occur**

- 286 The 'Extended Description' and 'Modes of Introduction' sections of each CWE entry provide

- 287 information on how an HW CWE can occur. The CWE Research Concepts view (<u>CWE-1000</u>)

- 288 organizes HW CWEs by abstractions of behavior. The path of nodes from the Research Concepts

- view root to the HW CWE under analysis describes how a weakness can occur with increasing

- 290 granularity as the path is traversed. Some HW CWEs have multiple paths that typically describe

- 291 simultaneously occurring behaviors and provide a more complete picture of how these CWEs

- 292 occur.

## 293 3.1.2. Determining Where Weaknesses Occur

- The Hardware Design view (<u>CWE-1194</u>) organizes the HW CWEs into 13 categories. They generally describe where an HW CWE can occur, potentially from different points of view (e.g.,

- physically on the chip, security operations, and life cycle). Section 5 describes each of these

- categories and the CWE classes associated with them. The 'Extended Description' of each CWE

- 298 is usually helpful in determining the "where."

## 299 **3.1.3. Determining What Damage Weaknesses Allow**

- 300 The CWE entry 'Common Consequences' section provides a high-level list of the security areas

- affected (e.g., access control, confidentiality, integrity, and availability) and the technical

- 302 impacts (e.g., read data, modify data, bypass access control). The 'Observed Examples' section

- 303 provides more granular and concrete damage explanations that are often useful for creating

- 304 failure scenarios. The 'Extended Description' section often discusses potential damage.

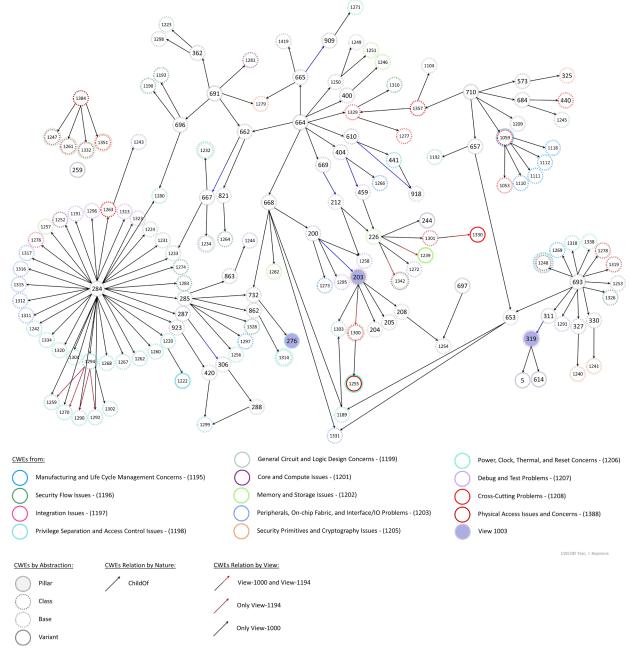

## 305 **3.2. Creating Hardware Weakness Subgraphs**

The failure scenarios are organized by their associated HW CWEs. The HW CWEs are primarily organized by the Research Concepts view (<u>CWE-1000</u>) and then secondarily by the Hardware

- 308 view (<u>CWE-1194</u>). This approach provides directed graphs that hierarchically show how HW

- 309 CWEs occur at increasing levels of granularity as the graph is traversed and additional

- 310 information is added about **where** the weaknesses can occur.

- 311 Figure 1 shows the complete HW CWE graph, all of the HW CWEs, and the non-HW CWEs

- 312 necessary to connect them together.

313 314

#### Fig. 1. Complete HW CWE graph created using View 1000 and View 1194

315 The HW CWE graph contains a root node for each of the seven Research Concepts view (<u>CWE-</u>

316 <u>1000</u> pillars that contain HW CWEs. It shows the Hardware Design view (<u>CWE-1194</u>) categories

- to which each CWE belongs and the view from which each relationship was defined. It also

- 318 shows the abstraction for each CWE pillar, class, base, and variant.

- 319 Section 4 shows the subgraphs of the CWEs reachable from each respective HW-associated

- 320 pillar. Appendix B provides an analysis and statistics for Fig. 1 and describes the algorithm used

- for the construction of the graphs. Appendix C through Appendix I provide an alternative

- 322 textual view of the pillar subtrees using a strict hierarchical tree layout. This latter approach is

- 323 convenient for a quick perusal of the HW CWEs but cannot capture the complex relationships

- that only become apparent from the complete graph view.

- 325 The HW CWE graphs in this publication primarily use arrows to show the relationships between

- the CWEs and colors to quickly provide additional information about each CWE (e.g., the HW

- 327 category it belongs to and the abstraction). For readers with difficulties discerning the colors,

- 328 this same information is available for each CWE on the associated CWE web page and can be

- 329 accessed using the format https://cwe.mitre.org/data/definitions/XXX.html, where XXX is

- 330 replaced with the CWE number.

331

## 332 **4. Hardware Security Failure Scenarios**

- 333 The HW security failure scenarios were created by reviewing the full CWE entries, extracting the

- three failure scenario aspects (the 'how', 'when', and 'what' from Sec. 3.1), and then writing a short summary of those aspects.

- This section contains an enumeration of 98 HW security failure scenarios distributed among the CWE pillars as follows:

- 338 1. Improper Access Control (<u>CWE-284</u>, 43 scenarios)

- 339 2. Improper Adherence to Coding Standards (<u>CWE-710</u>, 14 scenarios)

- 340 3. Improper Check or Handling of Exceptional Conditions (<u>CWE-703</u>, five scenarios)

- 341 4. Improper Control of a Resource Through its Lifetime (<u>CWE-664</u>, 40 scenarios)

- 342 5. Incorrect Comparison (<u>CWE-697</u>, one scenario)

- 343 6. Insufficient Control Flow Management (<u>CWE-691</u>, 11 scenarios)

- 344 7. Protection Mechanism Failure (<u>CWE-693</u>, 15 scenarios)

- The presence of a failure scenario in a product indicates the presence of the associatedweakness and an issue with one of the above pillars.

- 347 A small number of HW CWEs fall under multiple pillars. For these CWEs, the associated security

- failure scenario is located in the section for the pillar that qualitatively has the strongest linkage

- to the CWE. The full CWE Research Concepts view graph in Appendix B shows which HW CWEs

- are shared under which pillars.

- 351 The HW CWEs are grouped by the classes underlying the pillar. The CWE Research Concepts

- 352 view often provides finer grained delineations (e.g., organizing bases and variants under other

- 353 bases or providing subclasses under classes). For clarity of reading, this additional information is

- 354 provided in the associated figures for each subsection with directed subgraphs of the HW CWEs

- 355 under each pillar.

## 356 4.1. Improper Access Control

- 357 The CWE Improper Access Control (<u>CWE-284</u>) applies when a "product does not restrict or

- incorrectly restricts access to a resource from an unauthorized actor." Access control involves

the use of protection mechanisms, such as:

- Authentication (i.e., proving the identity of an actor)

- Authorization (i.e., ensuring that a given actor can access a resource)

- Accountability (i.e., tracking activities that were performed)

- The HW CWEs under this pillar occur within the following pillar/class hierarchy. The CWEs marked with \* are HW CWEs.

#### 365 CWE-284 P Improper Access Control

- 366 <u>CWE-1263</u> C Improper Physical Access Control \*

- 367 <u>CWE-1294</u> C Insecure Security Identifier Mechanism \*

- 368 <u>CWE-285</u> C Improper Authorization

- 369 Figure 2 shows the directed graph of HW CWEs under this pillar with their parent-child

- 370 relationships.

371 372

Fig. 2. HW CWE subgraph for pillar Improper Access Control (CWE-284)

- The HW class Improper Physical Access Control (<u>CWE-1263</u>) has one HW CWE child (<u>CWE-1243</u>).

The security failure scenario is:

- A malicious human can leverage physical access to obtain restricted information

because the physical security features are insufficient [CWE-1263].

- 377a. During debug operations, an untrusted agent can read security-sensitive device378information (e.g., encryption keys and manufacting data) that is permanently

- 379stored in fuses but loaded into protected registers due to code that does not380take the debug mode into account [CWE-1243].

- 381 The HW class Insecure Security Identifier Mechanism (<u>CWE-1294</u>) has five HW CWE children.

382 The security failure scenarios are:

- A malicious agent can initiate an unauthorized transaction (e.g., read, write, program, reset, fetch, compute) by taking advantage of incorrectly implemented security identifiers that define the privilege level of the agent in a system-on-a-chip (SoC) [<u>CWE-</u> 1294].

- a. A malicious agent on an SOC may assign itself inappropriate security tokens to

give itself additional privileges (e.g., read, write, fetch, program, compute, reset)

because the security tokens are improperly protected [<u>CWE-1259</u>].

- b. A malicious agent can gain inappropriate privileges over assets due to an

incorrect assignment of security tokens to agents. A single token may be

assigned to multiple agents, or multiple tokens may be assigned to a single agent

(CWE-1270).

- 394 c. A malicious agent can gain unauthorized access to an asset by taking advantage

395 of the incorrect decoding of security identifier information in bus-transaction

396 signals [<u>CWE-1290</u>].

- 397 d. An agent can gain unauthorized access to an asset by taking advantage of a

398 bridge incorrectly performing a protocol conversion between agents that use

399 different bus protocols [<u>CWE-1292</u>].

- 400 e. A security identifier is not included with an agent-to-agent transaction. This can

401 result in a denial of service (DoS) for the agent's requests or the ability of a

402 malicious agent to enact unauthorized actions due to inappropriate handling of

403 the missing identifier by the destination agent [CWE-1302].

- 404 The non-HW class Improper Authorization (<u>CWE-285</u>) has five security failure scenarios:

- Malicious software can take advantage of software-controllable device functionality

(e.g., power control, clock management, and memory access) to modify

registers/memory or to perform side-channel attacks without the need for physical

access to the chip [CWE-1256].

- 409

409

410

410

411

411

411

412

413

414

414

414

415

415

416

416

417

417

418

418

419

419

419

410

410

410

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

411

- An attacker can modify the hardware-stored firmware version number used in the

secure or verified boot process. The attacker can then execute older vulnerable versions

of firmware with plans to exploit known vulnerabilities and possibly prevent upgrades

[CWE-1328].

- 416 4. Malicious software can change non-write-protected parametric data values, thus

417 changing the unit conversion/scaling for sensor reporting (e.g., thermal, power, voltage,

- 418 current, and frequency). This can cause hardware to operate outside of design limits

419 even though the limit values themselves have not been modified [<u>CWE-1314</u>].

- 420 5. A human can use a physical debug or test interface to obtain sensitive information from

421 an asset due to an incorrect debug access level assignment [<u>CWE-1244</u>].

- There are 27 non-class HW CWEs that are direct children of pillar Improper Access Control

(<u>CWE-284</u>). The security failure scenarios are:

- An attacker with physical access to a chip can leverage a lack of or faults in debug/test

interface access control to read and set registers (e.g., via a scan chain using a Joint Test

Action Group [JTAG] interface) and bypass normal on-chip protections [CWE-1191].

- 427 2. Malicious code on a device may leverage a lack of granularity in hardware access control

428 to read or modify assets (e.g., device configuration and keys) by taking advantage of

429 unintended privileges [<u>CWE-1220</u>].

- 430

430

431

431

432

432

433

434

434

435

435

435

436

436

436

437

438

438

439

439

430

430

430

430

431

431

432

432

431

432

432

433

434

434

435

435

436

436

437

437

438

438

438

439

439

430

430

430

431

431

432

432

432

433

434

434

435

435

436

436

437

437

438

438

438

438

438

439

439

439

430

430

430

431

431

432

432

432

432

433

434

434

435

435

436

437

437

438

438

438

439

439

439

430

430

431

431

432

432

432

432

432

432

432

432

433

434

434

434

435

434

435

435

435

436

436

437

437

436

437

437

437

438

438

438

438

438

438

438

438

438

438

439

439

439

430

431

431

431

432

431

432

432

432

432

433

434

434

434

435

434

435

436

436

437

438

438

- 4. Malicious code can take advantage of an improper implementation of write-once

register bits to reprogram system settings (e.g., boot time configuration) [<u>CWE-1224</u>].

- 435 5. Attackers may unlock a secured system by leveraging design or code errors to modify

436 trusted lock bits that should have their values immutable after the initial set, thereby

437 enabling writes to protected registers or address regions [CWE-1231].

- 438

438

438

439

439

439

440

440

440

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

441

- Attackers can write malicious code to memory and then execute it because the central processing unit (CPU) does not support a bit that defines read-only and write-only regions of memory. This can also happen if the CPU relies on an improperly configured memory protection unit (MPU) and memory management unit (MMU) for read and write exclusivity [CWE-1252].

- 447 8. Attackers can access protected memory regions and perform both read and write by

448 using memory alias addresses (i.e., redundant addresses that point to the same memory

449 region) or mirrored memory regions that do not have the same protections. An attacker

450 could possibly create memory address aliases to perform such an attack [CWE-1257].

- 451 9. Lower privilege software can write to memory regions for higher privileged software

452 due to overlapping memory regions, thus enabling malicious software to perform

453 privilege escalation or a DoS attack [<u>CWE-1260</u>].

- 454 10. Malicious software can access registers that provide hardware functionality interfaces

455 due to an access control fault, allowing confidentiality and integrity violations [<u>CWE-</u>

456 <u>1262</u>].

- 457 11. A malicious agent on an SoC may gain inappropriate or even full access to another agent

458 when sending a bus transaction because the policy encoder mapping bus transactions to

459 security tokens uses an obsolete encoding [<u>CWE-1267</u>].

- 460

461

461

462

462

463

464

464

465

465

466

466

466

467

468

469

469

460

460

461

461

461

461

461

462

461

461

461

462

461

462

461

462

461

462

461

462

462

463

464

464

465

464

465

465

466

466

467

468

468

469

469

469

469

460

461

461

462

461

462

462

462

462

463

464

464

465

464

465

465

466

467

468

468

469

469

469

469

469

469

460

461

461

462

461

462

462

462

462

462

463

464

464

465

464

465

465

466

466

467

468

468

468

468

468

469

469

469

469

469

469

469

469

469

469

469

469

469

469

469

- 463

463 13. An attacker can change or replace boot loader code by leveraging inadequate access

464 control for the volatile memory (VM) in which the code is copied. This code is copied

465 from non-volatile memory (NVM) to VM and then authenticated by the SoC read-only

466 memory (ROM) code, but it is vulnerable to change after this occurs [<u>CWE-1274</u>].

- 467 14. Hardware intellectual property (IP) an independently developed component may

468 be improperly connected to its parent and result in security risks due to incorrectly

469 connected signaling. Functionality may be maintained but security weakened, enabling

470 unauthorized access by external agents [CWE-1276].

- 471 15. Malicious code can modify the registers containing the attestation data that measures

472 the boot code (i.e., secure hashes of the boot code), thereby enabling altered boot code

473 to be executed without being detected [CWE-1283].

- 474 16. A human can obtain unauthorized access permissions through a test access port (TAP)

475 or similar design element by leveraging logic errors that misconfigure the

476 interconnections of debug components [CWE-1296].

- 477 17. When a product is powering down, an attacker can modify the configuration state being

478 saved to persistent storage to alter the security or safety configuration upon restart

479 (e.g., modify privileges, disable protections, or damage hardware) [CWE-1304].

- 480 18. Malicious software can bypass access controls by leveraging a bridge between IP blocks

481 that use different fabric protocols (i.e., interconnecting components) that is incorrectly

482 translating security attributes from one protocol to another [CWE-1311].

- 483 19. An attacker can bypass a firewall in an on-chip fabric by writing to an unprotected

484 mirrored memory region that then propagates the changes to the original data [<u>CWE-</u>

485 <u>1312</u>].

- 486 20. An attacker can leverage a hardware feature that allows for the activation of test or

487 debug logic at runtime, thus enabling unauthorized reads and modifications to system

488 data and bus messages [<u>CWE-1313</u>].

- 489 21. A malicious IP responder in a fabric may initiate control transactions to other devices

490 through an incorrectly set register bit that allows an IP block to access other peripherals

491 [CWE-1315].

- 492 22. Protected and unprotected memory regions for an on-chip fabric may have overlapping

493 mappings (either accidentally or intentionally and maliciously) that enable an attacker to

494 send a transaction that modifies protected memory [<u>CWE-1316</u>].

- 495 23. An attacker can gain unauthorized access to an IP block by leveraging a lack of access

496 control checks by a fabric bridge that is translating transactions between two different

497 protocols [<u>CWE-1317</u>].

- 498 24. A malicious agent can cause hardware to operate outside of its design limits (potentially

499 causing physical damage) by disabling sensor alerts or initiate a DoS attack by

500 generating alerts. The attacker may also disrupt the response mechanism that receives

501 the alerts [CWE-1320].

- 502 25. An attacker can read security-sensitive traces (i.e., log data of IP blocks) from trace

503 aggregation IP blocks that either store this data in unprotected memory or allow

504 transport to unprivileged users (e.g., via a debug-trace port). These traces can include

505 instructions executed from a CPU, transaction types and destinations from a fabric, and

506 cryptographic keys from cryptographic coprocessors [CWE-1323].

- 507 26. An attacker can make unauthorized use of hardware error injection capabilities

508 (normally used for testing) to disrupt redundant IP blocks, thereby degrading

509 redundancy or forcing the IP component into a degraded operational mode [CWE-1334].

- 27. An attacker can bypass access control-protected assets by using unprotected alternate

paths (e.g., shadow registers and external interfaces) [<u>CWE-1299</u>].

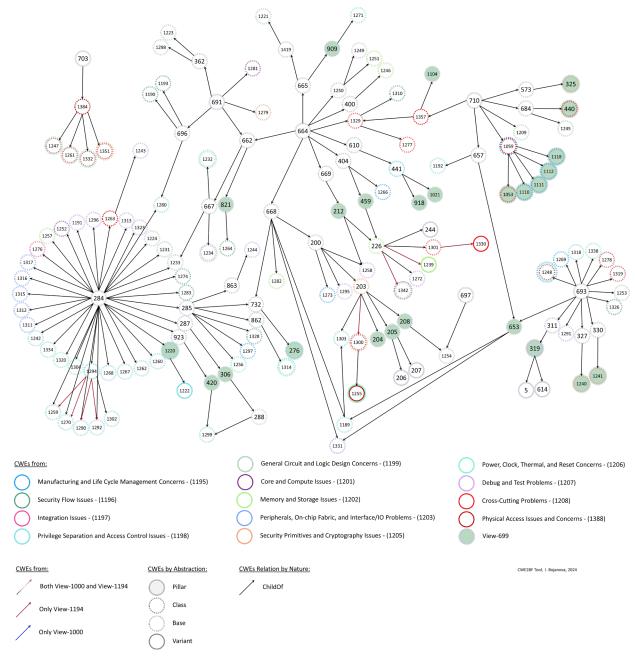

## 512 **4.2. Improper Adherence to Coding Standards**

- 513 The CWE Improper Adherence to Coding Standards (<u>CWE-710</u>) applies when a "product does

- not follow certain coding rules for development, which can lead to resultant weaknesses or

increase the severity of the associated vulnerabilities."

- 516 The HW CWEs under this pillar occur within the following pillar/class hierarchy. The CWEs 517 marked with \* are HW CWEs.

- 518 <u>CWE-710 P Improper Adherence to Coding Standards</u>

- 519 <u>CWE-573</u> C Improper Following of Specification by Caller

- 520 <u>CWE-684</u> C Incorrect Provision of Specified Functionality

- <u>CWE-1059</u> C Insufficient Technical Documentation \*

- <u>CWE-1357</u> C Reliance on Insufficiently Trustworthy Component \*

- 523 <u>CWE-657</u> C Violation of Secure Design Principles

- 524 Figure 3 shows the directed graph of HW CWEs under this pillar with their parent-child

- 525 relationships.

## 527

Fig. 3. HW CWE subgraph for pillar Improper Adherence to Coding Standards (CWE-710)

- 528 Under the non-HW class Improper Following of Specification by Caller (<u>CWE-573</u>), there is one 529 security failure scenario:

- An attacker can decipher cryptographic output because the cryptographic algorithm used by the IP block does not implement a required step [<u>CWE-325</u>].

- 532 Under the non-HW class Incorrect Provision of Specified Functionality (<u>CWE-684</u>), there are two 533 security failure scenarios:

- An attacker can compromise security due to an IP block that fails to perform according to its specification [<u>CWE-440</u>].

- Attackers can cause a DoS or possibly gain privileges by providing input to a finite state

machine (FSM) that drives it in an undefined state (the FSM code does not cover all

possible state transitions) [CWE-1245].

- No security failure scenarios were written for HW class Insufficient Technical Documentation

(<u>CWE-1059</u>) because it is too general to do so.

541 The HW class Reliance on Insufficiently Trustworthy Component (<u>CWE-1357</u>) has two security

542 failure scenarios:

- Attackers can compromise an SoC because it relies on the composition of IP blocks, one

of which is untrustworthy [<u>CWE-1357</u>].

- Attackers can compromise an SoC because it contains a vulnerable component that

cannot be updated (e.g., firmware or ROM used in secure booting) [<u>CWE-1329</u>] [<u>CWE-1329</u>]

<u>1277</u>] [<u>CWE-1310</u>].

- 548 Under the non-HW class Violation of Secure Design Principles (<u>CWE-657</u>), there are three 549 security failure scenarios:

- An attacker can gain unauthorized access to IP blocks if the secure operation of an SoC is

not achieved because the IP blocks are not securely and uniquely identified (e.g.,

missing, ignored, or insufficient identifiers) [CWE-1192].

- A malicious agent can access sensitive assets because multiplexed resources (e.g., pins that are used by both trusted and untrusted agents but not at the same time) do not properly isolate accessible assets (e.g., between trusted and untrusted agents) [<u>CWE-</u>

<u>1189</u>].

- An attacker can use timing channels to infer sensitive data when a network-on-chip

(NoC) does not provide proper isolation on the fabric and other resources between

trusted and untrusted agents [CWE-1331].

- 560 One non-class HW CWE is a direct child of pillar Improper Adherence to Coding Standards 561 (CWE-710). It has one security failure scenario:

- An attacker can compromise a hardware state by writing to reserved bits (i.e., unused

bits reserved for future functionality) that were covertly activated by developers for

debugging or undocumented capabilities [<u>CWE-1209</u>].

- 565 **4.3. Improper Check or Handling of Exceptional Conditions**

- The CWE Improper Adherence to Coding Standards (<u>CWE-703</u>) applies when a "product does

not properly anticipate or handle exceptional conditions that rarely occur during normal

operation of the product."

- 569 The HW CWEs under this pillar occur within the following pillar/class hierarchy. The CWEs

- 570 marked with \* are HW CWEs.

- 571 <u>CWE-703 P Improper Check or Handling of Exceptional Conditions</u>

- 572 <u>CWE-1384</u> C Improper Handling of Physical or Environmental Conditions \*

- 573 Figure 4 shows the digraph of hardware CWEs under this pillar with their parent-child

- 574 relationships.

NIST IR 8517 ipd (Initial Public Draft) June 2024

575 576

| 703<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384)<br>(1384 |                                            |        |                                                                                                                                                                                                                                                         |       |                                                                                                                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CWEs from:<br>Manufacturing and Life Cycle Management (<br>Security Flow Issues - (1196)<br>Integration Issues - (1197)<br>Privilege Separation and Access Control Issue                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | (                                          | 000000 | General Circuit and Logic Design Concerns - (1199)<br>Core and Compute Issues - (1201)<br>Memory and Storage Issues - (1202)<br>Peripherals, On-chip Fabric, and Interface/IO Problems - (1203)<br>Security Primitives and Cryptography Issues - (1205) | 00000 | Power, Clock, Thermal, and Reset Concerns - (1206)<br>Debug and Test Problems - (1207)<br>Cross-Cutting Problems - (1208)<br>Physical Access Issues and Concerns - (1388)<br>Not View-1194 |

| Both View-1000 and View-1194       Only View-1194       Only View-1000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ) Pillar<br>) Class<br>) Base<br>) Variant | /      | elation by Nature:<br>childof<br>ar Improper Adherence to Coding St                                                                                                                                                                                     |       | CW228' Tool, L Bajanova                                                                                                                                                                    |

577 The HW class Improper Handling of Physical or Environmental Conditions (<u>CWE-1384</u>) has five 578 security failure scenarios:

| 579<br>580<br>581<br>582 | 1. | or env<br>power | acker can leverage natural or maliciously created design-limit-exceeding physical<br>ironmental conditions (e.g., atmospheric, electromagnetic interference, lasers,<br>variance, overclocking, component aging, cosmic radiation) to compromise the<br>operations of a chip [ <u>CWE-1384</u> ]. |

|--------------------------|----|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 583<br>584<br>585        |    | a.              | An attacker can compromise security functionality (e.g., secure boot) by introducing voltage and clock glitches (this can also happen naturally) [ <u>CWE-</u> <u>1247</u> ].                                                                                                                     |

| 586<br>587               |    | b.              | An attacker can leverage the degradation of secure operations on a chip or a DoS due to single-event upsets (SEUs) (i.e., random bit flip errors) [ <u>CWE-1261</u> ].                                                                                                                            |

| 588<br>589               |    | с.              | An attacker can bypass security-critical code by using fault injection techniques to skip security-critical instructions [ <u>CWE-1332</u> ].                                                                                                                                                     |

| 590<br>591<br>592        |    | d.              | An attacker can cool hardware below the minimum design operating temperature to vary hardware behavior to compromise deployed security (e.g., power cycling not clearing volatile memory) [ <u>CWE-1351</u> ].                                                                                    |

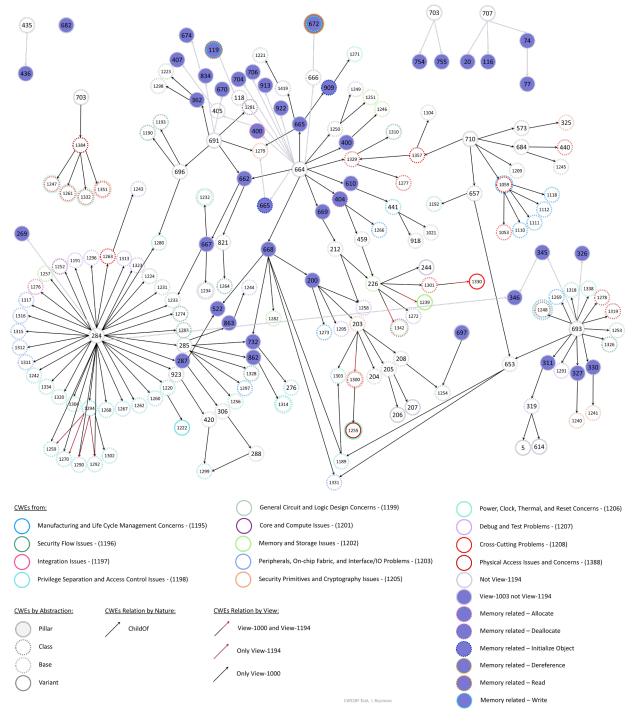

#### 593 **4.4. Improper Control of a Resource Through its Lifetime**

- 594 The CWE Improper Control of a Resource Through its Lifetime (<u>CWE-664</u>) applies when a

- 595 "product does not maintain or incorrectly maintains control over a resource throughout its596 lifetime of creation, use, and release."

- 597 The HW CWEs under this pillar occur within the following pillar/class hierarchy. No child class of 598 the pillar is itself an HW CWE.

- 599 <u>CWE-664 P Improper Control of a Resource Through its Lifetime</u>

- 600 <u>CWE-400</u> C Uncontrolled Resource Consumption

- 601 <u>CWE-404</u> C Improper Resource Shutdown or Release

- 602 <u>CWE-610</u> C Externally Controlled Reference to a Resource in Another Sphere

- 603 <u>CWE-662</u> C Improper Synchronization

- 604 <u>CWE-665</u> C Improper Initialization

- 605 <u>CWE-668</u> C Exposure of Resource to Wrong Sphere

- 606 <u>CWE-669</u> C Incorrect Resource Transfer Between Spheres

- Figure 5 shows the digraph of hardware CWEs under this pillar with their parent-childrelationships.

609 610

Fig. 5. HW CWE subgraph for pillar Improper Control of a Resource Through its Lifetime (CWE-664)

- 611 Under the non-HW class Uncontrolled Resource Consumption (<u>CWE-400</u>), there is one security

612 failure scenario:

- An attacker can cause a premature failure of NVM by taking advantage of non implemented or incorrectly implemented wear leveling operations (e.g., by repeated

writing) [<u>CWE-1246</u>].

- 616 Under the non-HW class Improper Resource Shutdown or Release (<u>CWE-404</u>), there is one

- 617 security failure scenario:

- 618

1. An attacker can retrieve sensitive information from decommissioned hardware that was

619 not scrubbed of sensitive information [<u>CWE-1266</u>].

- 620 Under the non-HW class Externally Controlled Reference to a Resource in Another Sphere

621 (<u>CWE-610</u>), there is one security failure scenario:

- An attacker can violate access control by sending a message to a hardware component

via an intermediary, whereby the message is interpreted by the recipient as having the

privileges of the intermediary (not the original unprivileged sender) [CWE-441].

- 625 Under the non-HW class Improper Synchronization (<u>CWE-662</u>), there are four security failure626 scenarios.

- An attacker can change system configuration information stored in lock-protected

registers after a power state transition that causes improper lock behavior (e.g., making

the lock programmable, clearing the lock, or resetting protected registers) [<u>CWE-1232</u>].

- An attacker can violate access controls by directly changing system configurations

protected by a register lock bit since the one-way lock that was properly set after

system startup does not prevent the changes [<u>CWE-1233</u>].

- An attacker can modify security-sensitive configuration information by using a debug

mode to remove lock bit protections [<u>CWE-1234</u>].

- An attacker can obtain access to sensitive data that is transmitted before security

approval by taking advantage of errors in the separate control and data channels in

hardware bus protocols [<u>CWE-1264</u>].

- 638 Under the non-HW class Improper Initialization (<u>CWE-665</u>), there are three security failure639 scenarios:

- An attacker can read cryptographic output by taking advantage of weakened or broken

cryptography that was encrypted before the cryptographic support units were ready

(e.g., an external random number generator) [CWE-1279].

- An attacker can compromise system security if register or IP parameter defaults

(initialized at hardware reset) are incorrectly hard-coded with insecure values in the

hardware description language code [CWE-1221].

- An attacker can violate system security by taking advantage of an uninitialized security critical register (e.g., before register initialization during system startup) [<u>CWE-1271</u>].

- 648 Under the non-HW class Exposure of Resource to Wrong Sphere (<u>CWE-668</u>), there are seven

649 security failure scenarios:

- An attacker can violate system security by changing security-sensitive and assumedimmutable data (e.g., golden digests) that are insecurely stored in writable memory instead of immutable memory (e.g., ROM, fuses, or one-time programmable memory

[OTP]) [CWE-1282].

- An attacker can unlock hardware (e.g., to enter debug mode) using leaked or stolen credentials that were often necessarily shared among multiple entities (e.g., for hardware products not created by a single company, via vertical integration) [<u>CWE-</u>

<u>1273</u>].

An attacker can obtain sensitive information from debug messages that unnecessarily

- An attacker can obtain sensitive information from debug messages that unnecessarily

reveal security details, often reducing security by obscurity (e.g., location of password

hashes) [<u>CWE-1295</u>].

- 4. An attacker can obtain security-relevant state information by observing different

behaviors that are indicative of the hardware state (e.g., in timing, responses, and

control flow) [<u>CWE-203</u>].

- An attacker can obtain security-sensitive information by leveraging physical access to

the hardware to measure phenomena (e.g., physical side channels, such as real-time

power consumption) [<u>CWE-1300</u>] [<u>CWE-1255</u>].

- 6. An attacker can obtain sensitive data by evaluating and probing shared

microarchitectural resources in contexts that should be isolated (e.g., caches and branch

prediction logic) [<u>CWE-1303</u>].

- 670