©Copyright by Attila Gürsoy 1994

# SIMPLIFIED EXPRESSION OF MESSAGE-DRIVEN PROGRAMS AND QUANTIFICATION OF THEIR IMPACT ON PERFORMANCE

# BY

# ATTILA GÜRSOY

B.Sc., Middle East Technical University, 1986M.S., Bilkent University, 1988

# THESIS

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer Science in the Graduate College of the University of Illinois at Urbana-Champaign, 1994

Urbana, Illinois

Communication latency and unpredictable delays in remote response times constitute significant impediments to achieving high performance on massively parallel computers. Message-driven execution is a promising technique to improve the performance of parallel computations by overlapping these delays with useful computation. This thesis explores message-driven execution for improving performance of parallel programs. Programming in message-driven style is difficult due to the split-phase transactions it requires and due to the nondeterministic arrival of messages. We developed language constructs to express dependences between messages and computations in order to simplify expression of message-driven programs. Predicting the performance of message-driven programs via simulations is difficult because the arrival order of messages changes as the machine characteristics change. We developed a trace-driven simulation methodology based on the those language constructs. We also conducted an extensive performance study of message-driven programs.

# ACKNOWLEDGEMENTS

I would first like to thank my advisor, Professor L.V. Kale, for his guidance and support during my doctoral research. He was a constant source of assistance, and his brilliant ideas were always stimulating. I also wish to thank Professor S.P. Vanka for being my co-advisor and for his support. I thank the other members of my committee: Professor M. Heath, D. Reed, and F. Saied, for their helpful recommendations.

Thanks to the members of the Parallel Programming Laboratory, including S.Krishnan, E.Kornkven, and A. Sinha, for providing a wonderful working environment and for listening to my practice presentations.

I also want to express my thanks to the Scientific and Technical Research Council of Turkey for providing me with the opportunity to pursue my doctoral studies at the University of Illinois.

Many of my friends deserve credit for their help. I would especially like to thank Maria Jose Gonzalez for her loving support and encouragement.

Finally, my profound thanks go to my parents: Ali and Ayşegül Gürsoy, and to my sister, Ayla Gürsoy. I cannot express with words how grateful I am for their constant support and love.

# TABLE OF CONTENTS

# Chapter

| 1 | Intr | roduction                                                                | 1   |

|---|------|--------------------------------------------------------------------------|-----|

|   | 1.1  | Remote information access latency                                        | . 2 |

|   | 1.2  | Reducing the impact of latency: message-driven execution                 |     |

|   | 1.3  | Thesis objectives                                                        |     |

|   |      | 1.3.1 Selection of computation domain for the performance study          |     |

|   | 1.4  | Main contribution of the thesis                                          |     |

|   | 1.5  | Thesis organization                                                      |     |

| 2 | Mes  | ssage-driven execution and Charm                                         | 10  |

|   | 2.1  | Traditional SPMD model                                                   |     |

|   |      | 2.1.1 Overlapping communication in SPMD                                  |     |

|   |      | 2.1.2 Traditional SPMD is inadequate to develop efficient large programs |     |

|   | 2.2  | Message-driven execution                                                 |     |

|   |      | 2.2.1 Message-driven execution supports modularity                       |     |

|   | 2.3  | The potential benefits of message-driven execution                       |     |

|   | 2.4  | Emulating message-driven style in SPMD                                   |     |

|   |      | 2.4.1 Using nested if blocks                                             |     |

|   |      | 2.4.2 Using a global while-switch loop                                   |     |

|   | 2.5  | Charm – a message-driven system                                          |     |

|   |      | 2.5.1 The Charm language                                                 |     |

|   |      | 2.5.2 The Charm runtime                                                  |     |

|   | 2.6  | Related work on latency tolerance                                        |     |

| 3 | Twe  | o obstacles                                                              | 31  |

|   | 3.1  | Programming difficulties of message-driven style                         |     |

|   |      | 3.1.1 Nondeterministic message arrival                                   |     |

|   |      | 3.1.2 Obscure flow of control                                            |     |

|   | 3.2  | Performance prediction: how to simulate message-driven computations      |     |

| 4 | Cor  | ntrolling the complexity of message-driven programs                      | 38  |

| _ | 4.1  | Divide-And-Conquer: a simpler context                                    |     |

|   |      | 4.1.1 Language definition                                                |     |

|   |      | 4.1.2 Data declarations                                                  |     |

|   |      | 4.1.3 Blocks                                                             |     |

|   |      | 4.1.4 Statements                                                         |     |

|   |      |                                                                          |     |

|   |              | 4.1.5 An example                                                |

|---|--------------|-----------------------------------------------------------------|

|   | 4.2          | Dagger                                                          |

|   |              | 4.2.1 Expecting a message                                       |

|   |              | 4.2.2 An example                                                |

|   |              | 4.2.3 Basic language                                            |

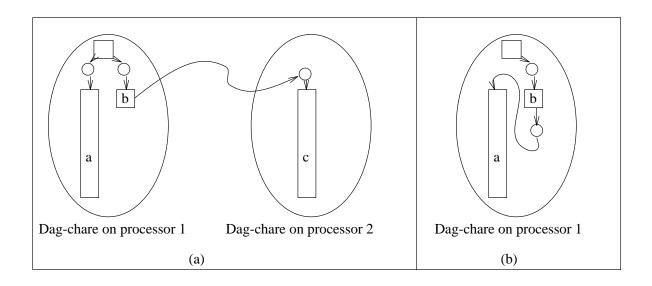

|   |              | 4.2.4 Dag-chare example                                         |

|   |              | 4.2.5 Extended language                                         |

|   |              | 4.2.6 Expressing loops in dag-chare                             |

|   |              | 4.2.7 Reference numbers                                         |

|   |              | 4.2.8 Pipelining independent iterations of a loop               |

|   |              | 4.2.9 Multiple message entry points                             |

|   |              | 4.2.10 Translation and runtime of Dagger                        |

|   | 4.3          | Message-driven libraries                                        |

|   | 4.0          | 4.3.1 Problems with libraries in SPMD style                     |

|   |              |                                                                 |

|   | 4 4          | 4.3.2 Message-driven execution and library interface techniques |

|   | 4.4          | Related work                                                    |

| 5 | Sim          | ulating message-driven programs                                 |

| J | 5.1          | Introduction                                                    |

|   | $5.1 \\ 5.2$ | A sufficient condition for accurate simulation                  |

|   | 5.2          | Dagger programs and automatic trace generation                  |

|   | 5.4          |                                                                 |

|   |              | The parallel machine model                                      |

|   | 5.5          | Simulator                                                       |

|   |              | 5.5.1 Preprocessor                                              |

|   |              | 5.5.2 Parallel machine simulator                                |

|   |              | 5.5.3 Interpreting the traces                                   |

| 6 | Per          | formance studies                                                |

| • | 6.1          | Description of benchmarks                                       |

|   | 0.1          | 6.1.1 Synthetic benchmarks                                      |

|   |              | 6.1.2 Concurrent reductions                                     |

|   |              | 6.1.3 Harlow-Welch                                              |

|   |              | 6.1.4 Conjugate Gradient                                        |

|   | 6.2          |                                                                 |

|   | 0.2          | 6.2.1 Synthetic benchmarks                                      |

|   |              |                                                                 |

|   |              |                                                                 |

|   |              | 6.2.3 Harlow-Welch                                              |

|   | 0.0          | 6.2.4 Conjugate Gradient                                        |

|   | 6.3          | Effects of coprocessor                                          |

|   | 6.4          | Random variations in latencies                                  |

|   | 6.5          | Load balance versus critical path                               |

|   |              | 6.5.1 Load balanced spanning trees and message-driven execution |

|   |              | 6.5.2 Complementary spanning trees for multiple reductions      |

|   | 6.6          | Effects of message scheduling                                   |

|   |              | 6.6.1 Preemptive scheduling                                     |

|   |              | 6.6.2 Priority-based scheduling                                 |

|                  | 6.7   | Conclu  | sion | <br> | • | <br>• | • | • | • | • | <br>• | • | • | <br>• | • | • | • | <br>• | • | • | • | • |   | <br>• | • | • | • | • | . ] | 152 |

|------------------|-------|---------|------|------|---|-------|---|---|---|---|-------|---|---|-------|---|---|---|-------|---|---|---|---|---|-------|---|---|---|---|-----|-----|

|                  |       | clusion |      |      |   |       |   |   |   |   |       |   |   |       |   |   |   |       |   |   |   |   |   |       |   |   |   |   |     |     |

|                  | 7.1   | Future  | work | <br> | • | <br>• | • | • | • | • | <br>٠ | • | • | <br>• | • | • | • | <br>• | • | • | • | • | • | <br>٠ | ٠ | • | • | • | . 1 | 157 |

| Bi               | bliog | raphy   |      | <br> |   |       | • |   |   |   | <br>• |   |   | <br>• | • |   | • |       |   |   |   |   |   |       |   |   |   | • | 1   | 159 |

| $\mathbf{V}^{i}$ | ita . |         |      |      |   |       |   |   |   |   |       |   |   |       |   |   |   |       |   |   |   |   |   |       |   |   |   |   | 1   | 168 |

# LIST OF TABLES

| 5.1 | Machine parameters                                            |

|-----|---------------------------------------------------------------|

| 5.2 | Events in a when-block trace                                  |

| 6.1 | CG results on NCUBE/2                                         |

| 6.2 | Communication parameters for the coprocessor experiment       |

| 6.3 | Communication parameter settings in the variable latency test |

| 6.4 | Effects of branching factor                                   |

| 6.5 | Effect of complementary spanning trees                        |

# LIST OF FIGURES

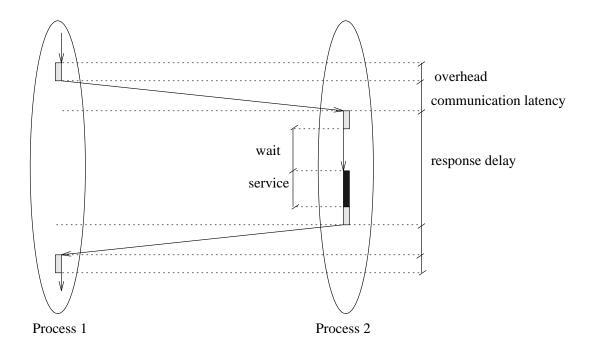

| 1.1  | Remote information access latency                                                   | 3  |

|------|-------------------------------------------------------------------------------------|----|

| 2.1  | Simple SPMD codes (a) with message passing primitives (b) with library/module calls | 12 |

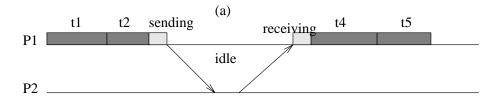

| 2.2  | Rearranging send and receives (a) a sample code (b) rearranged code                 |    |

| 2.3  | Processor utilization for (a) naive code (b) rearranged code                        |    |

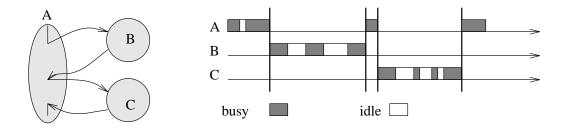

| 2.4  | SPMD modules cannot share the processor time                                        | 14 |

| 2.5  | Message-driven modules share the processor time                                     | 16 |

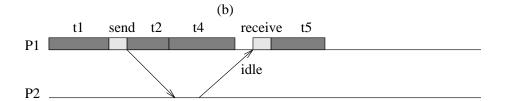

| 2.6  | s independent threads                                                               | 17 |

| 2.7  | Overlapping latency.                                                                | 17 |

| 2.8  | Latency tolerance                                                                   | 19 |

| 2.9  | Effect of overhead                                                                  |    |

| 2.10 | Using nested if's to simulate message-driven execution                              |    |

|      | A global while-switch construct to simulate message-driven execution                |    |

|      | Chare definition.                                                                   | 25 |

| 2.13 | A branch office – ring program                                                      | 26 |

|      | Multiple modules in Charm (a) module M2 accesses entities in module M1 (b)          |    |

|      | interface module for M1 M1.interface                                                | 28 |

| 3.1  | Incorrect message-driven code                                                       | 33 |

| 3.2  | Correct message-driven code                                                         |    |

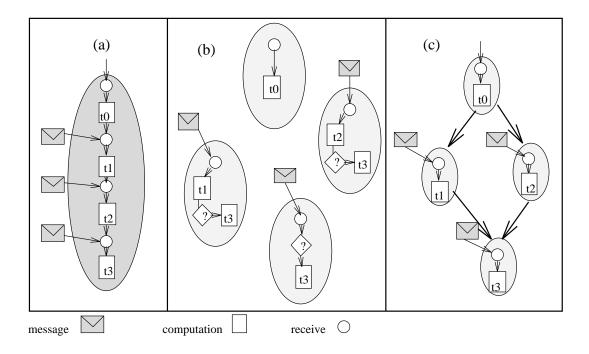

| 3.3  | Flow of control (a) SPMD (b) pure message-driven (c) partial order                  | 36 |

| 4.1  | Divide-and-conquer node definition                                                  | 41 |

| 4.2  | Node definition to compute Fibonacci numbers                                        | 43 |

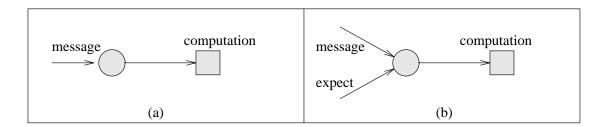

| 4.3  | A message triggers a computation (a) in pure message-driven (b) in Dagger           | 44 |

| 4.4  | Matrix multiplication chare                                                         | 46 |

| 4.5  | Matrix multiplication dag-chare                                                     |    |

| 4.6  | Dag-chare template                                                                  |    |

| 4.7  | Dag-chare illustrating adaptive overlapping                                         |    |

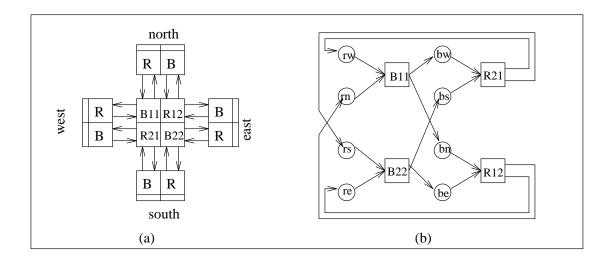

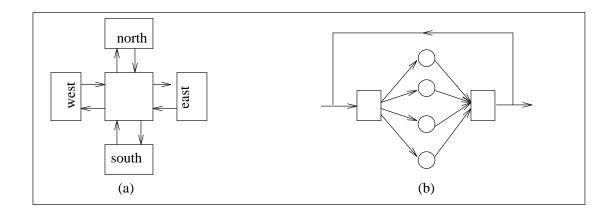

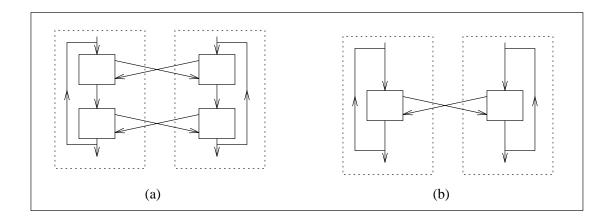

| 4.8  | Red-black Gauss-Seidel (a) partitions (b) dependences on one processor              |    |

| 4.9  | Dag-chare for Gauss-Seidel red-black relaxation                                     |    |

| 4.10 | Jacobi (a) partitioning (b) dependences on one processor                            |    |

|      | Partial dag-chare for Jacobi relaxation                                             |    |

|      | Out of order messages                                                               |    |

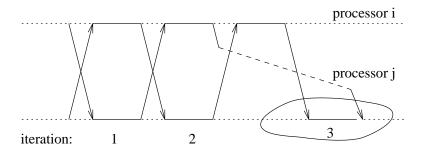

|      | Loop structure in (a) red-black (b) Jacobi                                          |    |

| 4.14 | Correct Jacobi relaxation with reference numbers                                    | 59 |

| 4.15           | Pipelining loop iterations                                                                                                                  | 60  |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.16           | A reduction dag-chare illustrating multiple message entries                                                                                 | 62  |

| 4.17           | Translation of a dag-chare                                                                                                                  | 63  |

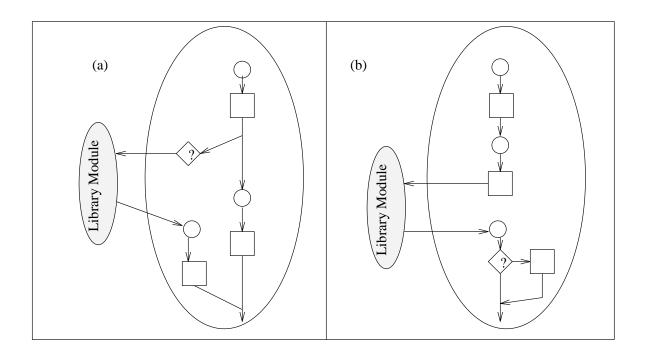

| 4.18           | Library call                                                                                                                                | 68  |

|                | Using the reduction library.                                                                                                                |     |

|                | Distributed Processes example                                                                                                               |     |

|                | Ada select statement                                                                                                                        |     |

|                |                                                                                                                                             |     |

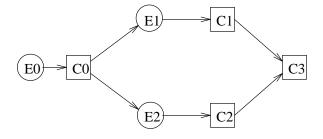

| 5.1            | A dag computation                                                                                                                           |     |

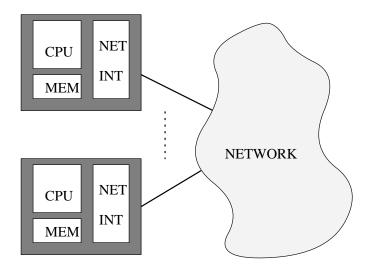

| 5.2            | The parallel machine                                                                                                                        |     |

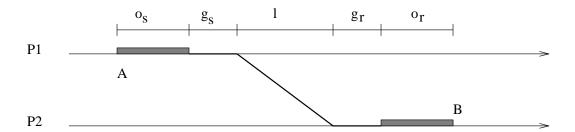

| 5.3            | Sending a message                                                                                                                           |     |

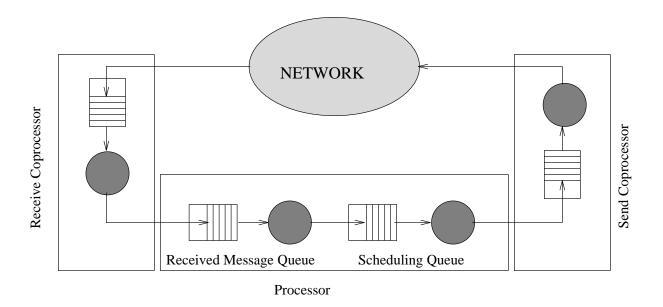

| 5.4            | Message queues                                                                                                                              |     |

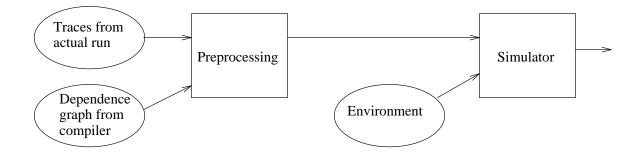

| 5.5            | Simulation system                                                                                                                           | 88  |

| 6.1            | Synthetic benchmark Wave (a) message-driven (b) SPMD                                                                                        | 95  |

| 6.2            | Synthetic benchmark Mlib (a) message-driven (b) SPMD                                                                                        |     |

| 6.3            | Concurrent reductions (a) SPMD (b) message-driven                                                                                           |     |

| 6.4            | Pipelining and effects of overhead.                                                                                                         |     |

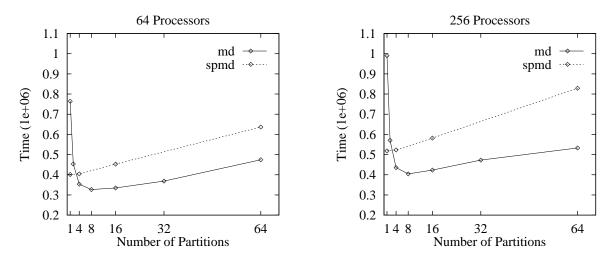

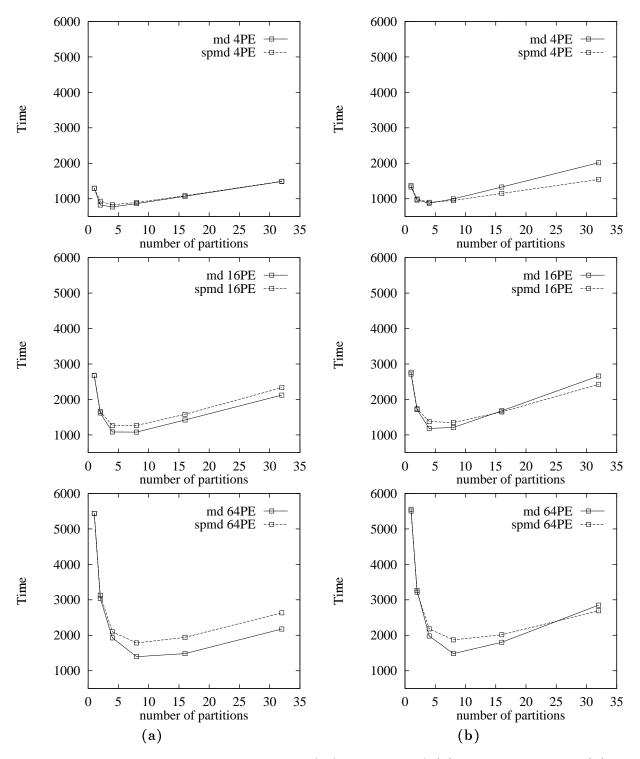

| 6.5            | Concurrent reductions: effect of number of partitions on NCUBE/2                                                                            |     |

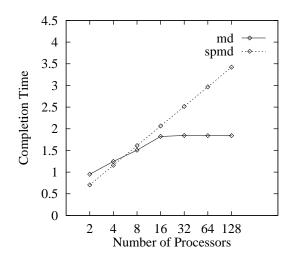

| 6.6            | Tolerating latency: concurrent reductions on NCUBE/2                                                                                        |     |

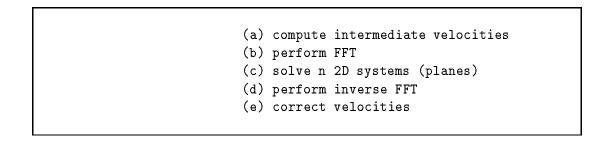

| 6.7            | One time step of Harlow-Welch algorithm                                                                                                     |     |

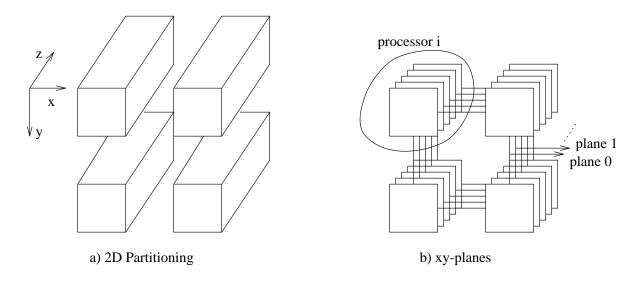

| 6.8            | Decomposition of the computational domain.                                                                                                  |     |

| 6.9            | Jacobi message-driven code                                                                                                                  |     |

|                | Red-Black1 message-driven code                                                                                                              |     |

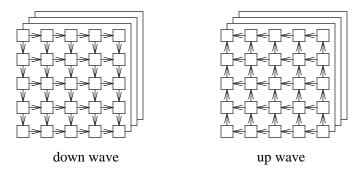

|                | Dependences of the Stone's method.                                                                                                          |     |

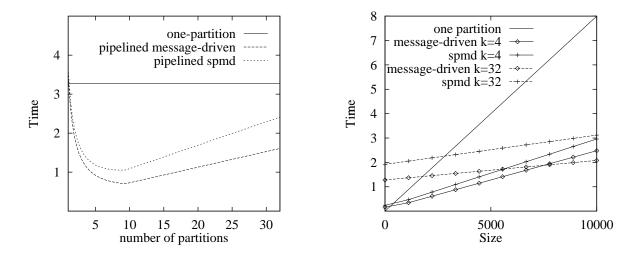

|                | Stone's method: effect of pipelining                                                                                                        |     |

|                | Stone's method on NCUBE/2 (times in msec) (a) without reductions (b) with                                                                   |     |

| 9              | reductions.                                                                                                                                 | 111 |

| 6.14           | Stone's method message-driven code                                                                                                          |     |

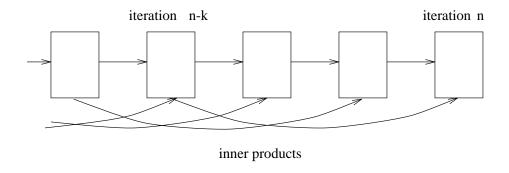

|                | Dependences in the modified CG method                                                                                                       |     |

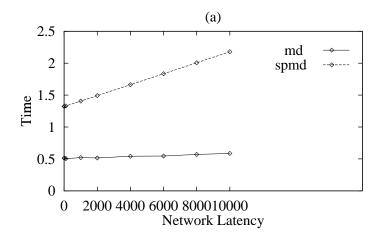

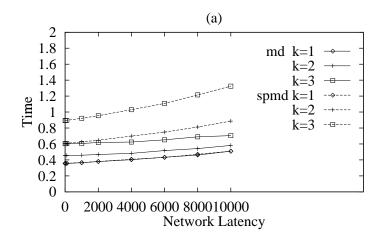

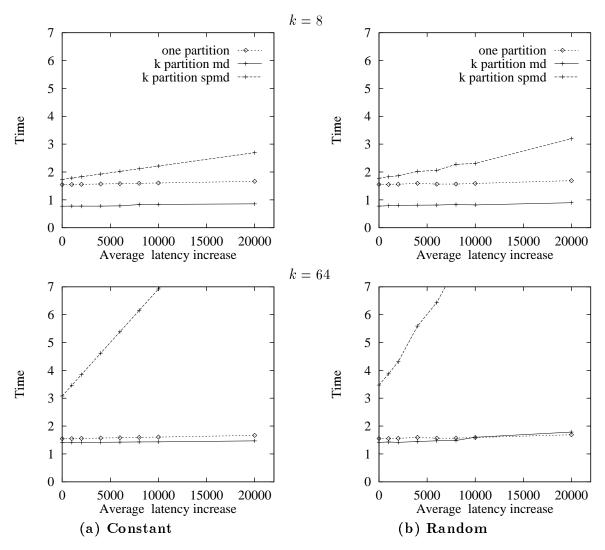

|                | Effects of network latency: Synthetic Wave                                                                                                  |     |

|                | Effects of network latency: Synthetic Mlib.                                                                                                 |     |

|                | Effects of network latency: Synthetic Mlib with varying computation load                                                                    |     |

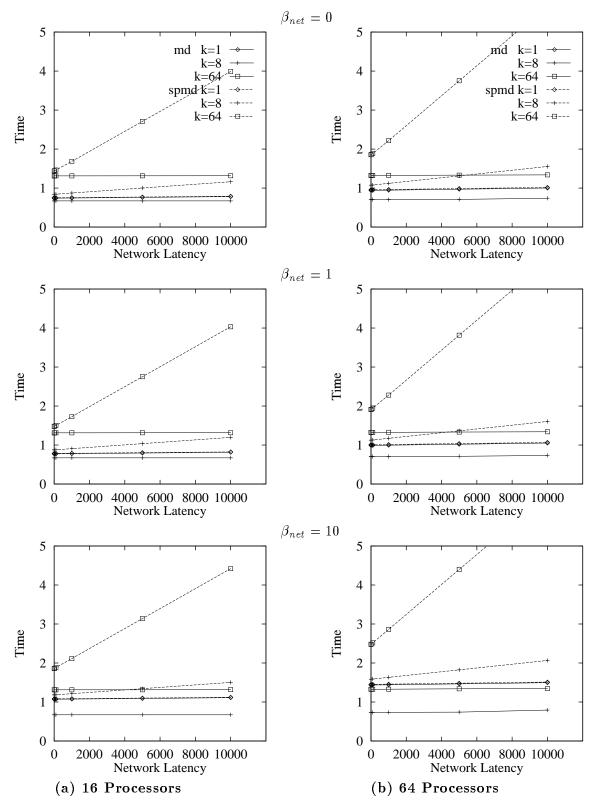

|                | Concurrent reductions: effect of network latency $\alpha_{net}$ , and $\beta_{net}$                                                         |     |

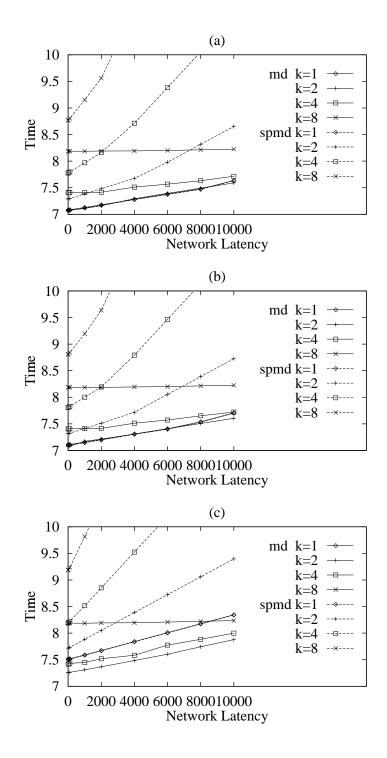

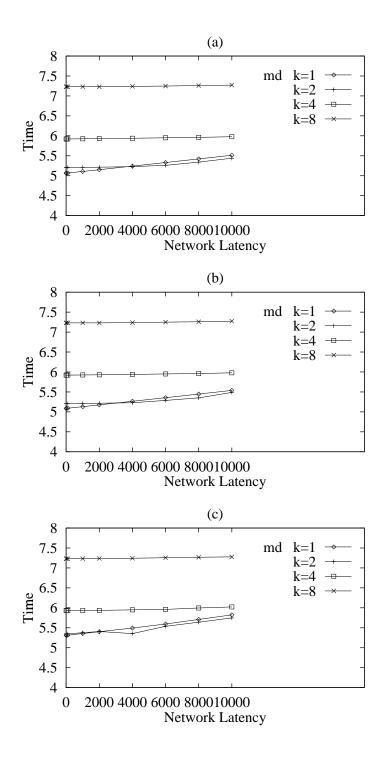

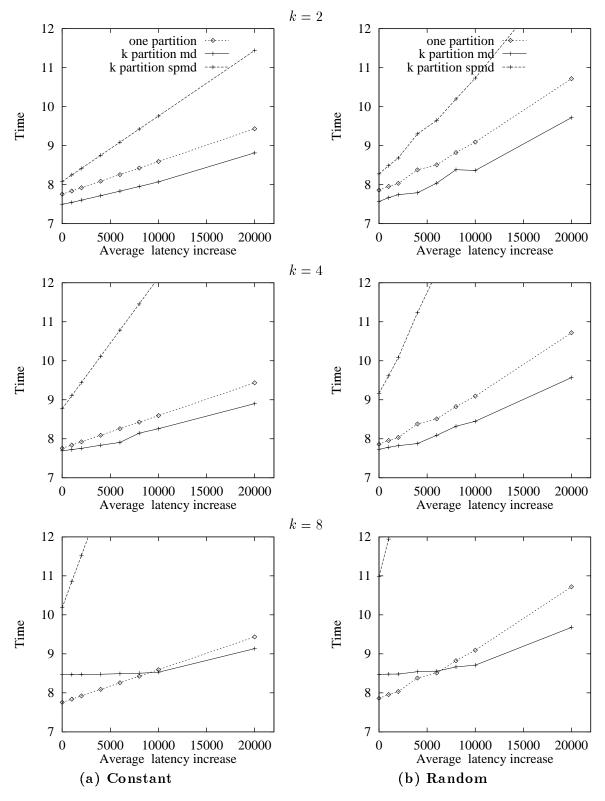

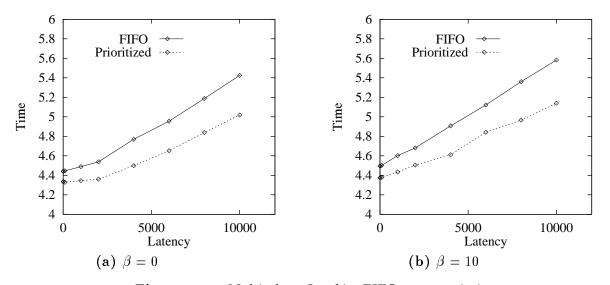

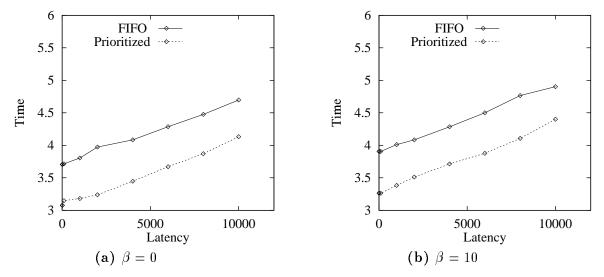

|                | Harlow Welch with Jacobi: effect of network latency $\alpha_{net}$ , and $\beta_{net}$ (a) $\beta_{net} = 0$                                |     |

|                |                                                                                                                                             | 120 |

| 6.21           | (b) $\beta_{net} = 1$ (c) $\beta_{net} = 10$ Harlow Welch with Red-Black1: effect of network latency $\alpha_{net}$ , and $\beta_{net}$ (a) |     |

| 5 · <b>2</b> - | $\beta_{net} = 0$ (b) $\beta_{net} = 1$ (c) $\beta_{net} = 10$                                                                              |     |

| 6 22           | Harlow Welch with Red-Black2: effect of network latency $\alpha_{net}$ , and $\beta_{net}$ (a)                                              |     |

| ·              | $eta_{net} = 0 \text{ (b) } eta_{net} = 1 \text{ (c) } eta_{net} = 10. \dots \dots \dots \dots \dots \dots \dots \dots$                     | 123 |

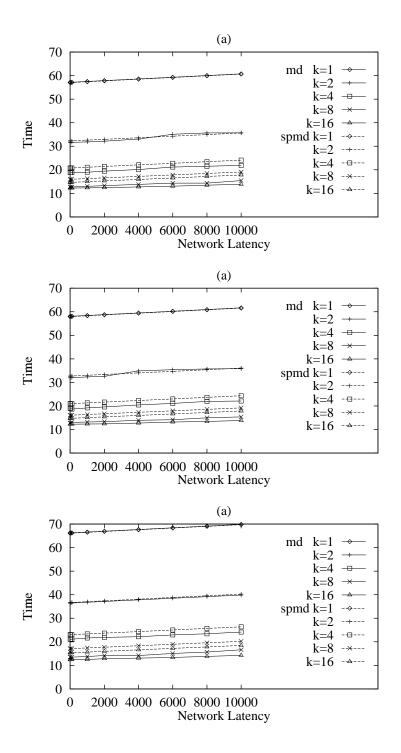

| 6.23           | Harlow Welch Stone: effect of network latency $\alpha_{net}$ , and $\beta_{net}$ (a) $\beta_{net} = 0$ (b)                                  |     |

| 0.20           | $eta_{net}=1\ (c)\ eta_{net}=10.\ \ldots\ldots\ldots\ldots\ldots$                                                                           | 125 |

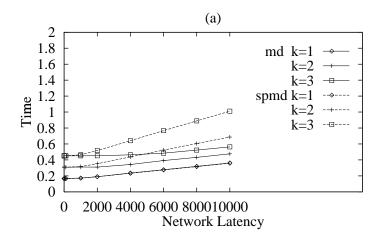

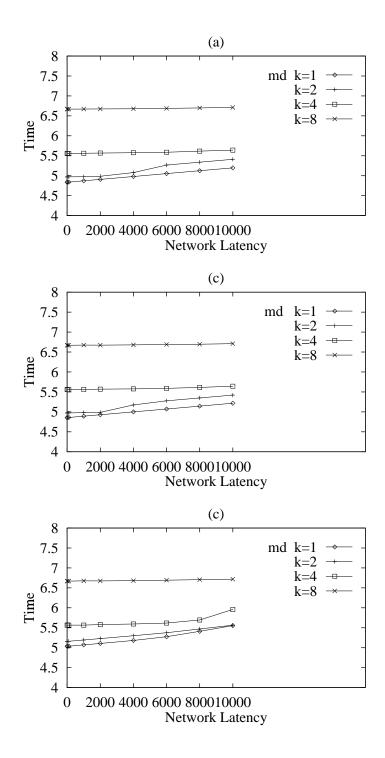

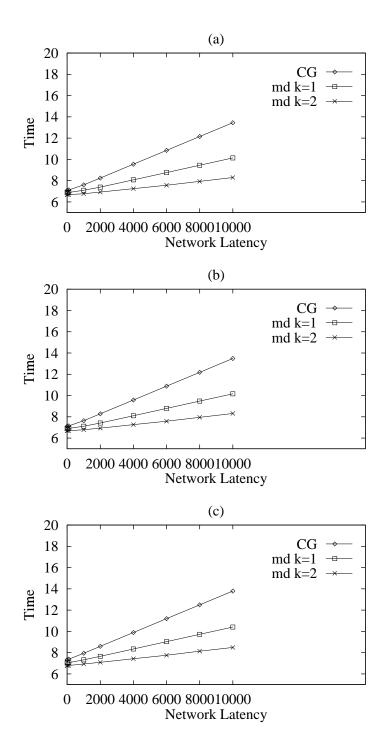

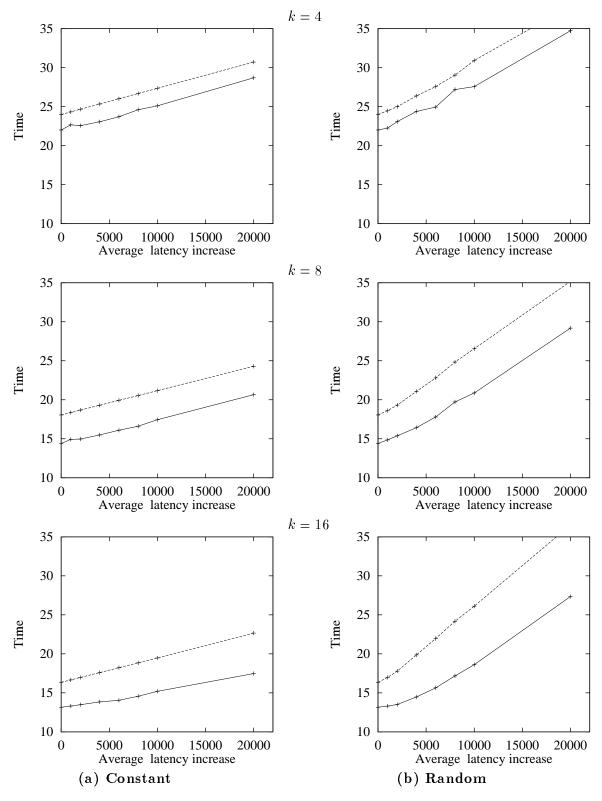

| 6.24           | Conjugate Gradient (model):effect of network latency $\alpha_{net}$ , and $\beta_{net}$ (a) $\beta_{net} = 0$                               | 0   |

| J 1            | (b) $\beta_{net} = 1$ (c) $\beta_{net} = 10.$                                                                                               | 126 |

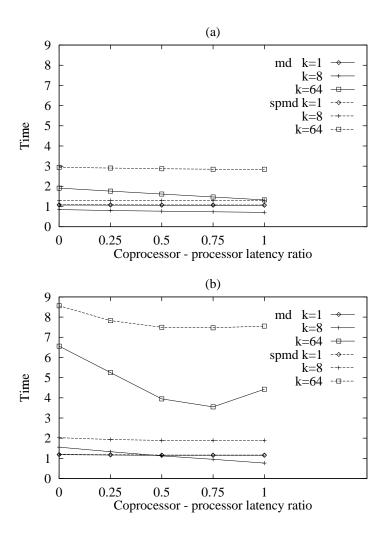

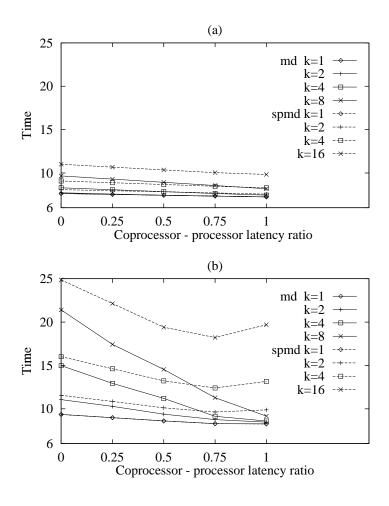

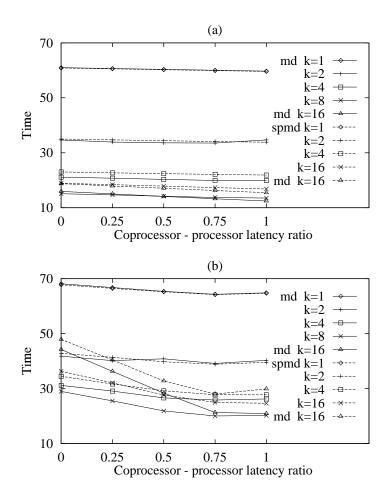

| 6.25           | Effect of the coprocessor - concurrent reductions. Sum of processor and copro-                                                              |     |

| J. <b>2</b> J  | cessor delays (a) 1000 (b) 10000 units                                                                                                      | 129 |

|                |                                                                                                                                             |     |

| 6.26 | Effect of the coprocessor - multiplane Jacobi. Sum of processor and coprocessor |

|------|---------------------------------------------------------------------------------|

|      | delays (a) 1000 (b) 10000 units                                                 |

| 6.27 | Effect of the coprocessor - multiplane Stone's method. Sum of processor and     |

|      | coprocessor delays (a) 1000 (b) 10000 units                                     |

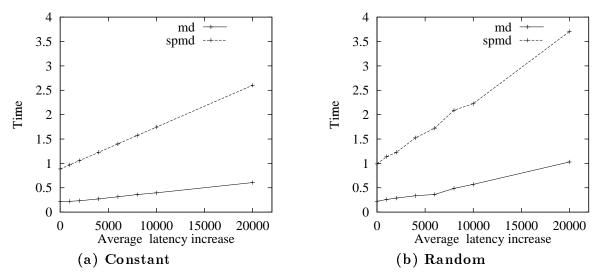

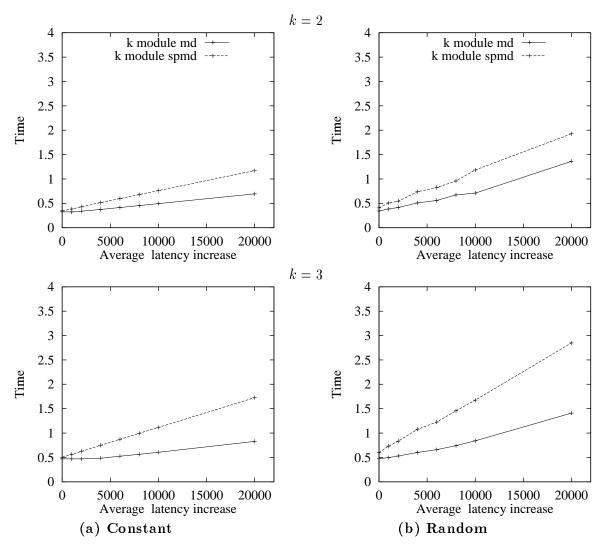

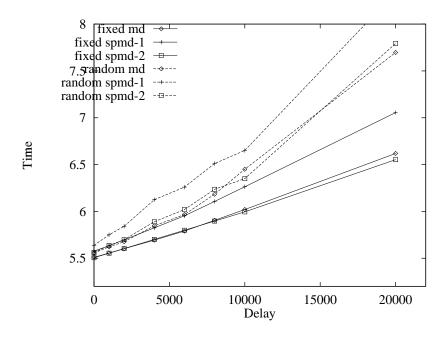

| 6.28 | Variable network latencies – Synthetic Wave                                     |

| 6.29 | Variable network latencies - Synthetic Mlib                                     |

| 6.30 | Variable network latencies – Concurrent reductions                              |

| 6.31 | Variable network latencies – Multiplane Jacobi                                  |

| 6.32 | Variable network latencies – Multiplane Stone                                   |

| 6.33 | Variable network latencies – One plane Red-Black2                               |

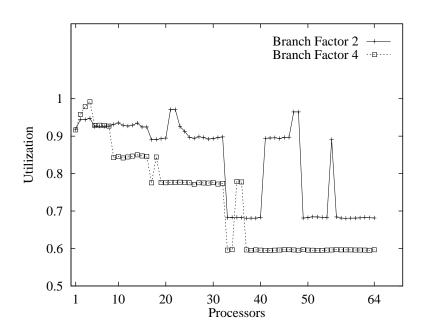

| 6.34 | Load balance of spanning trees                                                  |

| 6.35 | A scheduling problem                                                            |

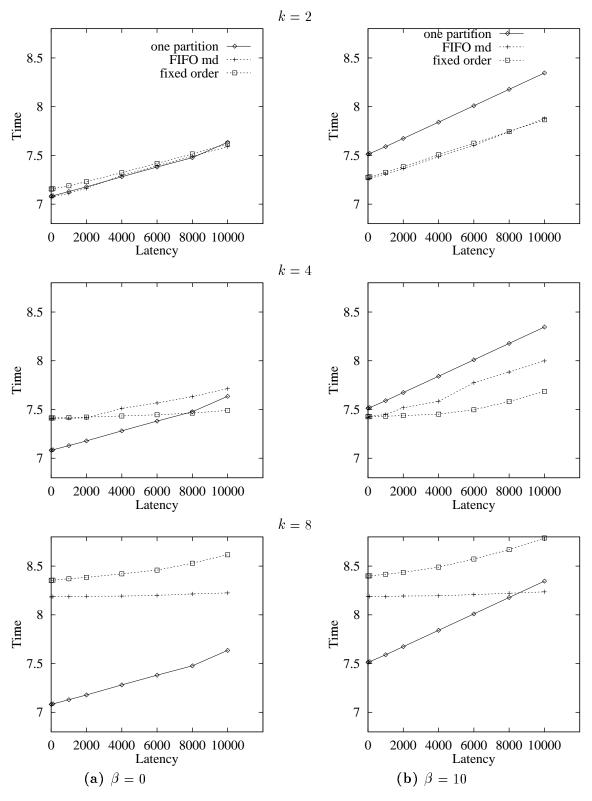

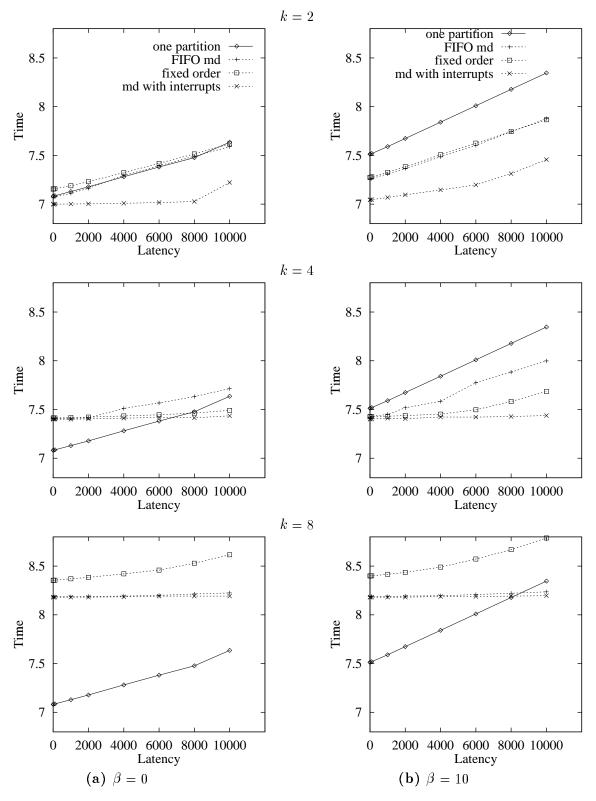

| 6.36 | Reductions with interrupts                                                      |

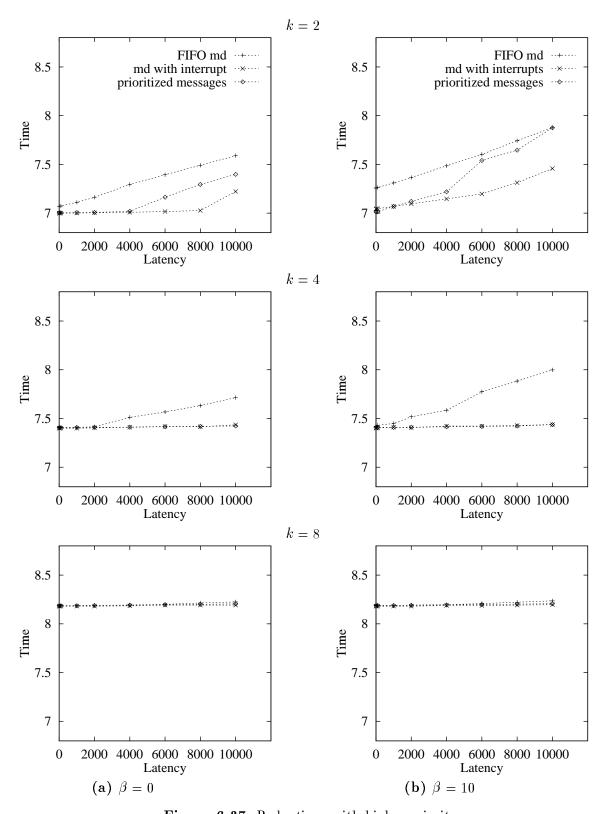

| 6.37 | Reductions with higher priority                                                 |

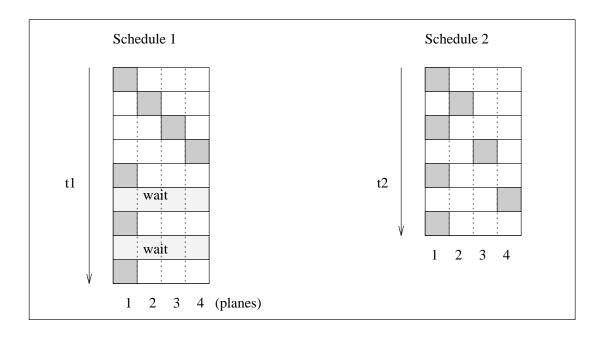

| 6.38 | Two different schedules                                                         |

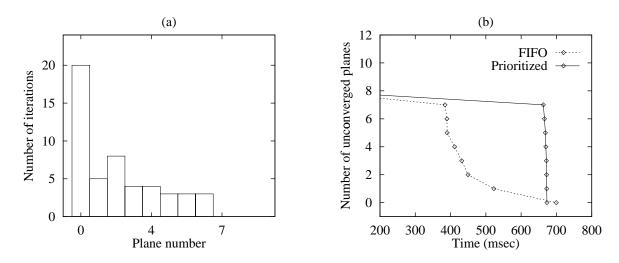

| 6.39 | Multi-plane Jacobi (a) load index (b) concurrency index                         |

| 6.40 | Multi-plane Jacobi: FIFO versus priority                                        |

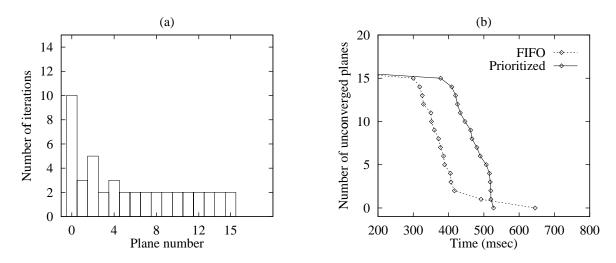

| 6.41 | Multi-plane Stone (a) load index (b) concurrency index                          |

|      | Multi-plane Stone: FIFO versus priority                                         |

|      | Greedy scheduling example (a) FIFO (b) forced static scheduling                 |

|      |                                                                                 |

# Chapter 1

# Introduction

Parallel computers potentially offer much more computational power than uniprocessor machines. Although recent advances in VLSI and microprocessor technology have improved the performance of uniprocessor systems, there are many problems that require computational power well beyond what uniprocessor systems can provide. Therefore, substantial effort is devoted to developing efficient and cost effective parallel machines.

Currently, there are many commercial parallel computers with very high peak performance. Machines with tens of gigaflops capacity are already available, and teraflops machines are expected in the next decade. However, their performance falls substantially short of peak on many real life applications. A number of factors contribute to this performance loss. For example, the sequential performance of individual processors itself may fall short of the peak power because of cache performance and inability to exploit fully features such as multiple instruction issues, pipelining, etc. Hopefully, this problem can be solved eventually by better compilers, use of optimized libraries such as BLAS routines [28], and occasional use of assembly code. In any case, this factor is not specific to parallel computing, as performance of workstations is also affected by it.

An important factor that is specific to parallel computing is the loss of performance due to communication latencies and processor idling due to load imbalances and critical paths. These factors and methods for overcoming them are the focus of this thesis.

# 1.1 Remote information access latency

A parallel computation is a collection of co-operating processes. The processes and data are distributed across the parallel machine. Typically, these concurrent processes interact with each other during the course of computation. This interaction might be due to synchronization or to data access. In either case, a process needs information that is created or stored by some other processes. If the needed information is on some other processor, then access to this remote information will be slower than that to local information. This slowdown generally occurs for two reasons.

One of the reasons is the delay introduced by the communication network. The communication networks of large private memory machines are usually multi-hop switching networks. Messages experience delay of transmission, routing, and buffering. This delay, which we will call communication delay, is defined as the time interval between the moment data enter into the communication network and the time the data become available at the destination.

The other source that contributes to the remote information access latency is the delay in the creation of the information at the remote site (Figure 1.1). Process 1 sends a request for some particular information. When process 2 receives the request, it performs the required service, creates the information and sends it back. The time interval between the arrival of the request and the completion of the requested service is the response delay. The response delay can be longer than the service time itself and is often unpredictable. For example, the processor might be scheduled for some other task, or cache performance might delay processing. Response delays take place not only in request-and-respond type of interaction; it equally affects prearranged communication (i.e., prepare-and-send) where no request is necessary.

These two types of delays together form the remote information access latency, simply referred to as *latency*. Minimizing the impact of this latency is a major objective in parallel programming on parallel machines, and particularly on massively parallel scalable machines.

# 1.2 Reducing the impact of latency: message-driven execution

The impact of latency can be reduced in several ways. On the hardware side, this is addressed by designing architectures that attempt to reduce the communication latency to the minimum. The ALLCACHE architecture of the KSR-1 machine, and the message-processor architecture

Figure 1.1: Remote information access latency.

of J-Machine [22] are examples of these attempts as well as the continuous evolution of communication hardware in the traditional architectures of Intel and NCUBE machines [77]. However, physical reality dictates that remote access will always be significantly slower than local access (overhead can be reduced by better operating system support such as Active messages [31], SUNMOS).

Since latency cannot be eliminated completely, one may try to minimize the number of remote data accesses. This requires the placement of computations and data to be reorganized so that data accesses are localized as much as possible [43, 92].

A complementary approach to reduce the impact of latency, on the software side, is to overlap the delay with some useful computation. This idea — doing something else useful while waiting for data — has been used at different levels in computer systems. Multiple functional units of a cpu may overlap independent operations. For example, while a floating-point computation unit is busy, the next instruction and data could be fetched from the memory. In the prevalent parallel programming paradigm (the traditional SPMD paradigm, see Section 2.1), such overlap is enhanced by moving sends earlier and moving receives later. However, this

strategy is not sufficiently adaptive to the eventualities that may arise at runtime (see Chapter 2).

Message-driven execution is a promising technique in this regard. In the message-driven execution style (which is distinct from message-passing), there are typically many processes per processor. A process does not block the processor on which it is running while trying to receive a message. Instead, the system activates a process when there is a message for it. This improves latency tolerance in two ways. First, when one process is waiting for data from a remote process, another ready process may be scheduled for execution. Second, even a single process may wait for multiple data items simultaneously, and continue execution whenever any of the expected items arrive. If there are multiple subcomputations, each with  $t_1$  and  $t_2$  running time respectively, the message-driven running time is  $t_1 + t_2 - t_{overlap}$  as explained in Chapter 2. As we will see later, this leads to adaptive overlap and modularity.

# 1.3 Thesis objectives

This thesis will explore the message-driven execution technique for tolerating communication latencies. The major objectives of this thesis are:

### Simplification of expression of message-driven execution:

Although message-driven execution imparts the benefits alluded to above, it often extracts a price in the form of apparent program complexity. The *split-phase* or *continuation-passing* style of programming that it requires is sometimes non-intuitive and obfuscates the flow of control. As the system may execute messages in the order it receives them (as opposed to a deterministic order imposed by sequential receive statements), the programmer must deal with all possible orderings of messages. This involves complex reasoning about which message-orderings will not arise, which are harmless, and which must be dealt with by buffering, counters, and flags. Therefore, it is desirable and important to simplify the expression of message-driven programs, possibly via new languages or annotations.

### Performance prediction of message-driven execution:

Predicting the performance of message-driven computations via simulations is necessary to evaluate the benefits of message driven execution under various machine characteristics. In such computations, the sequence in which messages are processed is not fully specified.

As a result, at runtime messages may be executed in different sequences depending on runtime conditions. This makes simulation and performance prediction of message-driven programs a challenging task.

# Evaluation of the performance impact of message driven execution:

The ability to overlap computation with communication provides message-driven execution with the potential to improve the performance of a parallel program. However, this potential benefit needs to be established by performance studies. Such performance studies will help to determine:

- the effectiveness of message-driven execution in increasing performance,

- the factors that influence the performance of message driven programs,

- the conditions under which these performance benefits are realizable.

### 1.3.1 Selection of computation domain for the performance study

The performance studies in this thesis involve simulation and real machine implementation of selected computations. For dynamic tree-structured computations such as heuristic search, divide-and-conquer, game tree search, and evaluation of functional and logic languages, the performance advantages of message-driven execution is intuitively quite clear. In such problems, the message-driven strategy can adapt to the unpredictable nature of communication latencies and computational variations better than the conventional message passing style. For example, while evaluating a node of an and-or tree, one cannot predict if the node will be a simple leaf node or will lead to a large subtree. The structure of the tree is data dependent and dynamic. Due to the unpredictable nature of parallelism, one must assign many tree nodes per processor. As each node has a complex behavior, it is natural to treat each node as an individual object. The system must then process every incoming message, decide whether it involves creation of a new object (i.e., creation of a node), or it is a response from one of the subproblems of an and-or tree node, and activate the corresponding node to process this message. Each node itself must be willing to accept solutions (or a failure to find solutions) for any one of the multiple subproblems it may have started and create new subproblems that may depend on such solutions. All of this naturally leads to message-driven style for implementation. For

these reasons, many researchers in these areas have used message driven-execution, implicitly or explicitly [19, 63, 82].

A more interesting question, therefore, is whether message-driven execution is beneficial for static computations — computations whose overall structure is known ahead of time. Therefore, investigating the performance advantages of message-driven execution for such computations will help answer an interesting and important question; if such advantages are established, it will lead to a stronger endorsement of the message-driven execution. Despite their static nature, communication latencies and their associated unpredictability make these computations potential candidates for message-driven execution.

Computational Fluid Dynamics (CFD) appears to be a proper area to conduct the performance studies because (a) many CFD algorithms have a static structure, and (b) it is an important application area for parallel computing. A review of many CFD applications reveals that many of them use a few numerical kernel algorithms that have regular computational and communication structure [4, 7, 10, 11, 24, 42, 75]. We chose a few of these core problems for our study as described in Chapter 6.

# 1.4 Main contribution of the thesis

- The thesis develops a set of arguments and lines of reasoning with examples highlighting the differences between SPMD and message-driven programs and argues for the potential advantages of message-driven execution.

- The thesis research involves development and implementation of a language, Dagger, for simplified expression of message-driven programs.

- A methodology is devised for trace-driven simulation of message-driven programs, and a simulator based upon it is implemented.

- The thesis includes an extensive performance study involving several synthetic and real benchmarks, and performance measurement on real machines as well as simulations with varying machine parameters.

The idea of message-driven execution was first proposed by Hewitt [53] and later was elaborated by Agha [1]. The work on dataflow also relates to the same idea at a finer grain and

at the hardware level. However, there has not been an extensive comparison of this approach with the now dominant message passing model (receive based SPMD model that is elaborated in Chapter 2). We argue that modularity and efficiency – in the form of overlapping communication with computation – can be achieved much more easily in message-driven execution than in the traditional message passing paradigm. We also show why it is not adequate to emulate message-driven execution with the message passing style. Section 2.6 discusses other approaches related to message-driven execution with the Charm system. Charm was one of the first message-driven systems and is used as an implementation substrate in this thesis.

Programming in message-driven style is difficult due to the split-phase style of programming it requires and due to the nondeterministic arrival of messages. Therefore, the synchronization of messages and subcomputations in a process is necessary to maintain the integrity of the computation. Dagger expresses the partial orders among subcomputations and messages within an object, and yet retains the advantages of message-driven execution (adaptive scheduling of subcomputations based on message arrivals).

The issue of synchronization has been dealt with extensively in past research starting from the mid 1970's. However, many of the schemes require the caller of a method to block until the called object finished its service. In most of these approaches, the server is also blocked in a variety of contexts. None of these features can be used effectively to express adaptive overlap of different computations based on availability of data, which is an important requirement for message-driven execution. The distributed process model by Hansen [50] comes closest to Dagger in many respects. This model as well as others are compared to Dagger in Section 4.4. More recent work on the Actor model and other concurrent object oriented languages also address the issue of local synchronization within an object. These studies were also summarized in Section 4.4.

Although trace-driven simulation is a very efficient method for predicting performance of parallel programs under varying runtime conditions, such simulation methodology has not been applied to message-driven programs or to programs that use wild-card receives. The basic difficulty in such simulations is the fact that if two messages are received in different orders under different runtime conditions, then the behavior of the program may be altered in a way that cannot be reconstructed based on the traces obtained with the first sequence. The thesis presents a methodology for simulation of message-driven programs that exploits the

dependence information provided by Dagger at compile time combined with a special method for obtaining runtime traces. We know of no other results that can carry out performance analysis or simulations in a trace driven manner for such programs. Further, existing systems do not handle the case of a different message ordering during simulation.

The thesis includes an extensive performance study involving several synthetic and real benchmarks, and performance measurement on real machines as well as simulations with varying machine parameters. This study establishes the performance advantages of message-driven execution clearly and quantifies its benefits and cases in which these are realized. It also leads to new criteria for algorithm design for message-driven programs and emphasizes the importance of message scheduling.

# 1.5 Thesis organization

The thesis is organized as follows. Chapter 2 discusses and contrasts message passing and message-driven paradigms. It establishes preliminary evidence for the utility of message-driven execution. The Charm language, a message-driven system that we have chosen as a medium for this study, is presented. Chapter 3 elaborates difficulties encountered using the message driven style. These difficulties center around programming complexity and performance prediction via simulations. Chapter 4 describes the techniques we have developed as a part of this thesis for simplifying message-driven programming. These involve design and implementation of coordination languages to control the programming complexity. A coordination language to support message-driven computations in simpler contexts such as functional (divide-and-conquer) computations is described, as well as the Dagger language which allows easier expression of general purpose message-driven programs. Chapter 4 continues with the discussion of message-driven libraries. Libraries, in general, ease program development. Issues involved in the interface between libraries and programs in a message-driven environment are discussed. Dagger also provides a basis to carry out trace-driven simulations of such programs, eliminating the difficulty discussed in Chapter 3. Chapter 5 describes a trace-driven simulation methodology for message driven computations. The information necessary to carry out such simulations is identified, and a method for extracting such information from Dagger programs during compile-time and program execution is described. A general and parameterized model of parallel machines embodied

in the simulator is discussed. In Chapter 6, we evaluate the performance of message-driven computations on the selected problems. The evaluation is carried out with simulations and real machine implementations. The impact of latency on message-driven and message-passing implementations of the selected problems is observed, and the effect of various runtime conditions and parameters on their behavior is studied. The chapter concludes with message-driven algorithm design techniques that help improve the performance of message-driven algorithms. Chapter 7 presents conclusions.

# Chapter 2

# Message-driven execution and Charm

This thesis is concerned mainly with distributed-memory machines and with explicitly parallel programming. Most large parallel machines currently available are distributed-memory machines, such as nCUBE/2, CM-5, Intel/Paragon (although there are also large scalable shared-memory machines, such as KSR/1).

There are many programming models for programming parallel machines. A data parallel programming model with languages such as Fortran D and HPF [35] is useful for array-oriented applications. There are also parallel languages such as functional and logical languages that can be used to program these machines. However, neither of these models is general enough to apply easily to a broad class of applications, and therefore explicitly parallel languages are widely used. In explicitly parallel languages, the programmer explicitly specifies the partitioning of the application into parallel parts and often the mapping of the parts to processors. Such parallel languages include Linda [14], with a specialized or idiosyncratic programming model. However, the predominant paradigm used for programming parallel machines is provided by the traditional SPMD model, which is supported by vendors of parallel machines in their operating systems. Even data parallel and functional languages are often implemented using the traditional SPMD model as their backend.

This chapter will examine the traditional SPMD model and show its inadequacies in dealing with communication latency and adaptive overlap. It will elaborate on the message-driven

execution model and show how it can handle latency better, and will motivate, using analysis of a simplified computation model, the potential benefits of message-driven execution. It is possible to emulate message-driven execution within the extended SPMD style programming using asynchronous receives. How this can be done, and why this is not an adequate solution is shown in Section 2.4. Instead, a language that incorporates message-driven execution in its model is better suited for this purpose. Charm, a message-driven language, is used as a substrate for the work in the rest of the thesis. Other message-driven languages, as well as other related techniques for tolerating communication latencies, are described in Section 2.6.

# 2.1 Traditional SPMD model

The SPMD — single program multiple data — model simplifies program development by using a simple model for internal synchronization and scheduling. The phrase SPMD has been used with somewhat different meanings by different authors [40, 43, 69, 80, 84]. In the SPMD model, as used in this thesis, there is one process per processor (usually all processes are executing the same program). Communication among processes (hence processors) is usually with blocking primitives. Messages have tags, and the receive primitive blocks the processor until a message with a specified tag arrives (of course, there is no reason not to use non-blocking communication occasionally if it does not complicate the code). Moreover, we use "traditional SPMD model" to mean strict usage of blocking receives.

A single thread of control and blocking receives makes the programming of these machines relatively easy. Most of the synchronization requirements of the computation are handled implicitly by the blocking receives. For example, consider the code in Figure 2.1-(a). The computation of t1 and t2 needs the remote information a and b. Since the recv statements will not allow the processor to proceed until the required messages are received and made available to the code, the correct computation of t1,t2 and t3 is guaranteed.

# 2.1.1 Overlapping communication in SPMD

The simplicity of the flow-of-control attained in SPMD is at the expense of idling processors. After issuing a blocking receive, the processor must wait idly for the specified message to arrive. This wait may not always be dictated by the algorithm, *i.e.*, the algorithm may have more

```

(a)

t0 = h()

recv(tag1,a);

recv(tag2,b);

t1 = f(a);

t2 = f(b);

recv(tag3,c);

t3 = g(t1,t2,c)

```

```

(b)

comp1();

call fft();

call sum();

comp2();

```

Figure 2.1: Simple SPMD codes (a) with message passing primitives (b) with library/module calls.

relaxed synchronization requirements. Yet the usage of blocking primitives forces unnecessary synchronization and may cause idle time.

This idle time can be decreased by rearranging the send and receive operations. This involves moving the sends ahead and postponing the receives as much as possible in the code, as illustrated by the following example. A sample SPMD code is shown in Figure 2.2-(a). The code has a pre-communication phase (t1,t2) and a post-communication phase (t4,t5). Between these computation phases, it communicates with some remote processors by sending and receiving messages. This type of structure is common in SPMD programs that are either written by a programmer or automatically generated by a compiler [40]. The utilization of a processor during the execution of this code is shown in Figure 2.3-(a). The code is running on processor P1. After completing t1 and t2, the send is initiated. Then the processor starts the receive operation, which blocks the processor. Therefore, processor P1 is forced to stay idle during the communication latency of both send and receive operations (Although the algorithm does not require the first call to g to wait for the recv to finish, the blocking semantic of recv forces this synchronization).

Figure 2.2-(b) shows the rearranged code that overlaps the communications latency with some useful computation. The data dependencies among the computations reveal that the send can be issued just after the computation of t1, and t3 is needed only for the computation of t5. Figure 2.3-(b) shows the processor utilization after moving the send and receives appropriately. Processor P1 initiates sending the message and continues with the computation of t2 and t4 while the message transfer continues in the communication network. The remote processor

```

(a)

t1 = f()

t2 = f()

send(tag1,t1)

recv(tag1,t3)

t4 = g(t1,t2)

t5 = g(t1,t3)

```

```

(b)

t1 = f()

send(tag1,t1)

t2 = f()

t4 = g(t1,t2)

recv(tag1,t3)

t5 = g(t1,t3)

```

Figure 2.2: Rearranging send and receives (a) a sample code (b) rearranged code.

Figure 2.3: Processor utilization for (a) naive code (b) rearranged code.

P2 receives the message (request) and responds with the result message. The latency of this message is overlapped by the computation t4 on processor P1 since it invokes the receive operation after t4.

For this simple example, the local rearrangement of communication achieves the desired objective – increasing the utilization of processors. However, this strategy cannot handle cases with more complex dependencies and unpredictable latencies. For example, consider again the code in Figure 2.1-(a). The code contains two receives followed by computations t1,t2, and t3. t1 and t2 are independent of each other and need data from different receives. One of the receives can be postponed to overlap latency of the other one. If the latencies for these receives

Figure 2.4: SPMD modules cannot share the processor time.

are known a priori, then the one with longer latency may be postponed. However, in general, unpredictable communication delays make it difficult to know the latencies in advance. In case of such unpredictability, if the one that is postponed turns out to be the wrong one at runtime, then the idle time on the processor would be the same as the time for the original code. Thus, the SPMD model cannot adapt to such runtime conditions by rearranging the send and receive operations.

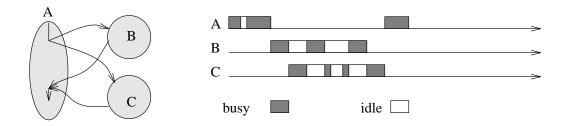

# 2.1.2 Traditional SPMD is inadequate to develop efficient large programs

Although SPMD model can achieve limited performance improvements as discussed in the previous section, it cannot overlap computation and communication across modules and libraries. A module or library is defined as an independently developed program that can be called from other programs, as in Figure 2.1-(b), which invokes two modules (fft and sum). In the SPMD style, invocation of another module passes the flow of control to that module. Until that module returns control, the calling program cannot do anything. Therefore, the idle times that a module experiences cannot be overlapped with computation from another module<sup>1</sup>. In Figure 2.4, for example, module A invokes two other modules B and C. Module A cannot activate B and C concurrently even if the computations in B and C are independent of each other. As a result, the processor time is not fully utilized, as illustrated in the same figure.

Notice that this problem is independent of communication latency. Even if communication latency were to be zero, each of the modules may have idle times on individual processors due to critical paths and load imbalances in them.

<sup>&</sup>lt;sup>1</sup>See Section 2.4 for a discussion of how one can use non-blocking message passing primitives for this purpose in SPMD style and why this is not adequate

Despite its simplicity, the traditional SPMD model is far from being a programming model for developing efficient large parallel applications for these reasons. The message-driven execution helps to solve these problems.

# 2.2 Message-driven execution

Message-driven execution, in contrast to the SPMD model, supports many small processes (or objects) per processor. These processes are activated by the availability of messages that are directed to them. At this level of description, it suffices to say that each process has a state and a set of functions (methods) for dealing with incoming messages. When a message arrives for a particular process, the system eventually activates the process. Then the process, depending on the content and type of the message, executes the appropriate method.

The system has a pool of incoming messages, because during the execution of a previous process many messages may have arrived. After a process suspends itself, the system selects one of the messages from the pool to be processed next. This selection procedure – message scheduling – can be a simple strategy such as FIFO, or can be a more complex strategy such as prioritized scheduling.

### 2.2.1 Message-driven execution supports modularity

Message-driven execution overcomes the two difficulties experienced by the SPMD model. It can effectively overlap latency with useful computation adaptively:

- within a module

- across the modules

The rearrangement of send and receives in SPMD, for example, failed to achieve the overlap adaptively (the example in Figure 2.2). Message-driven execution could compute either t1 or t2 in Figure 2.1-(a) depending on which message arrived first (or whichever message is made available for processing by the message-scheduler), hence, adapting itself to the runtime conditions. The computation of t3, however, now requires internal synchronization necessitated by message-driven style (i.e., it can be computed only after t1 and t2 are both calculated). We will discuss a method for expressing such synchronization in the next chapter.

Figure 2.5: Message-driven modules share the processor time.

The message-driven paradigm, in addition, allows different modules that might have some concurrent computations to share processor time. Consider the computation discussed in Section 2.1.2. Assuming that modules B and C do not depend on each other, the idle times on a processor can be utilized by another module if it has some work to do. Such a scenario is illustrated in Figure 2.5. Module C gets processor time (by virtue of having its message selected by the scheduler) while B waits for some data, and vice versa, thus achieving a better overlap than the SPMD program in Figure 2.4.

# 2.3 The potential benefits of message-driven execution

A performance analysis of a simple application model of message-driven execution is now developed to motivate the performance benefits of message-driven execution.

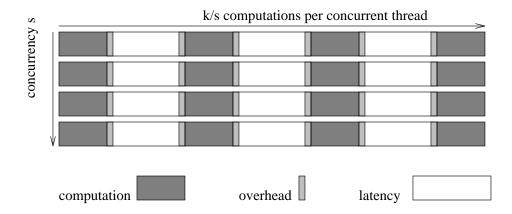

In this model, each processor performs k computations. Each computation is of length  $t_p$  time units and issues one remote data access at the end (sending and receiving a message). Each remote access has a latency of l time units. Some of these computations can be executed concurrently, as they do not depend on each other. The number of such concurrent computations is denoted by s, as illustrated in Figure 2.6. In practice, these s concurrent computations may arise at a particular time due to independent computations within a module or computations from different modules.

In the SPMD model, these computations will be executed sequentially because, as explained previously, the SPMD model is not adaptive to variations in latencies and blocks for receives, and it does not allow computations from different modules to be interleaved. Therefore, it is reasonable to assume that after every computation of length  $t_p$ , in the SPMD style, the processor blocks for l time units. The completion time of the whole computation for SPMD

Figure 2.6: s independent threads.

Figure 2.7: Overlapping latency.

can be written as:

$$T_{SPMD} = k(t_p + l)$$

Message-driven execution, on the other hand, is capable of activating any computation that is ready to be executed. In order to model message-driven execution, one more parameter,  $t_o$ , is introduced to reflect the additional overhead of message-driven execution. This overhead is due to context switching and message buffering required during the execution of the program.

The completion time for the message-driven case depends on how much of the latency is overlapped. If all of the latency is overlapped with useful computation, then the completion time would be  $k(t_p + t_o)$ . This happens if the latency is less than the time required to complete s concurrent computations. If the latency is larger than that, then the time to complete s concurrent computations will be  $t_p + l$ , where  $t_p$  is the time required for the first computation out of s computations. The time for the other s-1 computations will be masked by this latency. Therefore, the completion time for the message-driven case is:

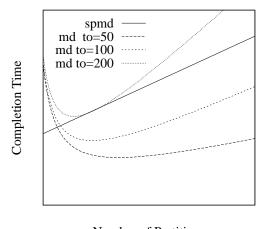

$$T_{md} = \begin{cases} k(t_p + t_o) & \text{if } s > \frac{l + t_p}{t_p + t_o} \\ \frac{k}{s}(t_p + l) & \text{otherwise} \end{cases}$$

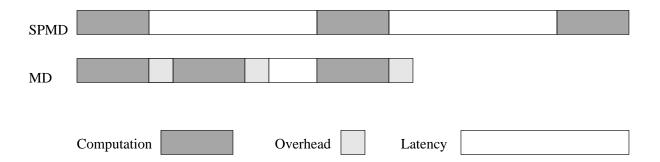

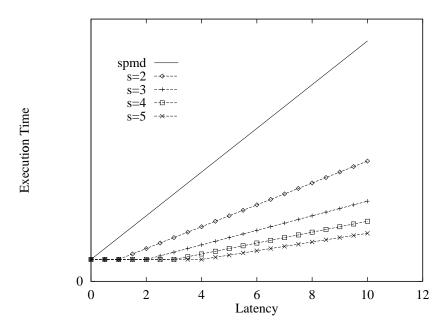

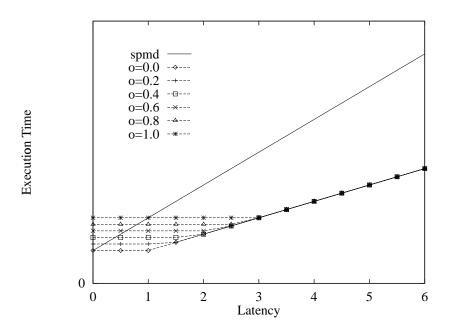

In order to determine the effects of the latency, the completion time of the model is plotted versus latency in Figure 2.8 for both SPMD and message-driven style. The overhead  $t_o$  for the message-driven execution has been kept zero. The latency is in terms of the computation time. The plot shows the latency tolerance curves for different concurrencies, s. There are a number of important observations here. The completion time of the message-driven execution remains constant as the latency increases up to a certain point, while the time for the SPMD version increases linearly with the latency. In the flat phase of the message-driven version (*i.e.*, the region left of the knee), message-driven execution completely overlaps the latency with computations. When the latency becomes too large, then the performance of the message-driven execution also degrades. However, it is asymptotically still better than the SPMD in the sense that the slope of the curve is lower, because it continues to overlap some parts of the latency.

In the second graph, Figure 2.9, the effects of the overhead are plotted. In this case, s is kept fixed and completion time curves for different values of  $t_o$  are plotted against the latency.

Figure 2.8: Latency tolerance.

The effect of overhead is an upward shift in the first phase (the phases where the latency is small enough to overlap completely). However, for larger latencies, the overhead is absorbed in the latency time also.

This simple model shows that it is worthwhile exploring message-driven execution for developing parallel algorithms. However, there are numerous factors affecting performance that this model has ignored, such as the scheduling policy, irregular computation times and latencies, and unbalanced load. To predict the performance of message-driven computations under these conditions becomes very difficult, if not impossible, with analytical methods. What is needed is an empirical study of the potential benefits of message-driven execution over a range of architectural parameters and application programs. Such a study is one of the foci of this thesis. To this end, we have developed a simulation framework to study the performance of message-driven computations more accurately (see Chapter 5).

Figure 2.9: Effect of overhead.

# 2.4 Emulating message-driven style in SPMD

We have defined message-driven execution and shown its potential performance benefits. In this section, we will discuss how message-driven execution can be emulated within the SPMD context and examine the adequacy of such an emulation.

The emulation of message-driven execution involves usage of nonblocking message passing primitives, particularly the nonblocking receive primitive. The examples presented in this section will use a primitive operation called *probe* and the blocking receive primitive instead of nonblocking receive. The *probe(tag1)* function checks if a message with the tag *tag1* has arrived. A probe followed by a blocking receive (if probe succeeds) is equivalent to nonblocking receive for our purposes.

# 2.4.1 Using nested if blocks

A simple approach to incorporate message-driven ideas in SPMD programs is to use nested if statements and nonblocking receives to replace some of the "blocking receive and compute" sequences. These sequences are the part of the code where the rearrangement of receives does not help for dynamic situations – as in the example of Section 2.1.1.

To illustrate this, the SPMD code in Figure 2.1-(a) is rewritten as shown in Figure 2.10. The if statement in the modified code first checks whether the message with tag tag1 has arrived. If the message has arrived, it computes t1 and blocks to receive the message with tag tag2. After this message arrives, it computes t2. However, the messages may arrive in the reverse order. Therefore, in the case the message tag1 has not arrived, the else part of the if repeats the same thing for the reverse order. If both messages have not arrived yet, the code must wait until they arrive (while statement) in order to continue with the rest of the code (computation of t3). The while loop must assure that both t1 and t2 have been computed in order to compute t3. This requires synchronization variables and/or counters. In this simple dependency case, a flag, not\_done, is sufficient. However, in general, the synchronization can be quite complicated by the dependencies among the receives and computations. In addition, the complexity of the loop increases with the number of concurrent receives. In general, if there are n receives, then the code must handle n! permutations of receive sequences. Finally, this approach will not take full advantage of message-driven execution since these if code-blocks will be scattered around the code and the computations across the if code-blocks cannot be executed concurrently. For these reasons, the nested if approach is not sufficient to exploit the full power of message-driven execution.

# 2.4.2 Using a global while-switch loop

A more structured approach to approximate message-driven style is to use a global while-switch construct in a module as shown in the Figure 2.11. This approach requires the SPMD program to be decomposed into code-blocks (functions f1(),...,fn()) such that these functions can be executed upon receiving a particular message. The processor continuously checks if a message (with any tag) has arrived. Whenever a message arrives, the processor invokes the appropriate code-block, depending on the tag of the message. A simple (and clear) application of this strategy is when the SPMD program can be decomposed into functions such that each one depends on a single message and there are no dependencies among the functions. Otherwise (i.e., in the presence of complex dependencies), the functions or the loop itself have to be augmented with all the synchronization constructs. As a result, the code would not appear as readable as the one in the example. Although the global while-switch loop appears to

```

t0 = h()

not_done = TRUE

while (not_done)

if (probe(tag1)) {

recv(tag1,a)

t1 = f(a)

recv(tag2,b)

t2 = f(b)

not_done = FALSE

else if (probe(tag2)) {

recv(tag2,b)

t2 = f(b)

recv(tag1,a)

t1 = f(a)

not_done = FALSE

recv(tag3,c)

t3 = g(t1,t2,c)

```

Figure 2.10: Using nested if's to simulate message-driven execution.

```

while (TRUE) {

if (probe(any_message_tag))

switch (message_tag) {

case tag1 : recv(tag1,m); f1(m);

case tag2 : recv(tag2,m); f2(m);

...

case tagn : recv(tagn,m); fn(m);

}

}

```

Figure 2.11: A global while-switch construct to simulate message-driven execution.

be more powerful than the nested if approximation, it still has some fundamental limitations. These limitations can be summarized as follows:

- Difficulty in supporting multiple modules: Every module must know the entities in other modules to prevent conflicts. Such global entities include the tags of messages defined in different modules. Adding a new message tag requires knowing all of the tags used across the modules, which destroys modularity. The recently proposed MPI message massing interface [36] solves this tag problem by providing the notion of contexts. Another name conflict is the function names. Again, the modules must use different names for a multiple module compilation. These two name conflicts destroy modularity in the compiling phase.

- Centralized changes: Any change in the modules, such as addition of more messages, may result in modifying the global loop structure. One may try to provide one individualized loop per module to increase modularity. But then, passing the flow of control across modules becomes difficult (the example discussed in Section 2.1.2). When module B receives a message that belongs to module C, then it should call the appropriate function in C. This further complicates a modular design of message-driven programs.

- **Dependencies must be reflected in the loop:** The dependencies among the functions and messages must be handled either inside the function or in the loop, presenting a further programming difficulty.

- No message scheduling: The basic while-switch loop has no scheduling control strategy.

The messages are processed in the order in which the processor provides them to the global loop (which is FIFO).

- Difficulty in supporting dynamic objects (computations): Finally, this approach in SPMD does not support dynamic creations of objects (here the functions with their local state).

These limitations prevent the SPMD approach from being a programming model for developing large, efficient parallel applications. A message-driven language seems to be a better method for developing such applications. However, such a pick-and-process message loop is a step in the right direction. In fact, such loops are used in the underlying implementation (or runtime system) of message-driven languages, which are often done on top of an SPMD system.

A programmer, in the absence of a message-driven language, should use such a loop to derive the performance benefits of message-driven execution.

# 2.5 Charm – a message-driven system

Charm is a C-based portable parallel programming system that consists of a language and a runtime system. The system allows one to define processes or objects and manages dynamic creation of processes with user-selectable load balancing or scheduling strategies. We will discuss the Charm language in some detail because the rest of the work requires some knowledge of Charm. More detailed information on Charm can be found in the manual and various papers on the subject [32, 60, 61].

# 2.5.1 The Charm language

A Charm program is a collection of processes (called chares) and messages. The chares are potentially small-grained message-driven objects. They have a state and they react to messages with different behavior. At any time, many chares may exist on each processor, or only a few, depending on the application.

### 2.5.1.1 Chare definition

A chare definition consists of local variable declarations, entry point definitions, and private function definitions as illustrated in Figure 2.12. Local variables of a chare are shared among the chare's entry-points and private functions. Private functions are not visible to other chares and can be called only inside the owner chare. Messages are sent to and received at the entry-points. An entry-point consists of a message definition of certain type and a code-block. The code-block can access the message by the name defined in the message definition.

Some of the important Charm system calls are:

### CreateChare(chareName,entryPoint,msg)

This call is used to create an instance of a chare named as chareName. As all other Charm system calls, CreateChare is a non-blocking call, that is, it immediately returns. Eventually, as the system creates an instance of chare chareName, it starts to execute the entryPoint with the message msg.

```

chare chare-name {

local variable declarations

entry EP1 : (message MSGTYPE *msgptr) {C code block}

..

entry EPn : (message MSGTYPE *msgptr) {C code-block}

private function-1() {C code block}

..

private function-m() {C code block }

}

```

Figure 2.12: Chare definition.

### SendMsg(entryPoint,msg,chareID)

This call deposits the message msg to be sent to the entryPoint of chare instance chareID. chareID represents an instance of a chare. It is obtained by a system call MyChareID(), and it may be passed to other chares in messages.

# 2.5.1.2 Replicated objects: branch office chares

A branch office chare (BOC) is a form of chare that is replicated on all processors. An instance of a BOC has a branch chare on every processor. A BOC definition is similar to a chare definition (with the BranchOffice keyword). In addition to the features of regular chares, a BOC contains public functions which can be called by other chares on the same processor. Also, it can send and broadcast messages to the branches of the same instance with the calls SendMsgBranch and BroadcastMsgBranch.

### 2.5.1.3 A Charm example

A simple Charm example is given. The rest of the thesis uses the Charm language, therefore a simple Charm program example will make it easier to understand the other examples.

This example, Figure 2.13, is a branch office chare that implements a ring communication where processor 0 sends a message to 1, then 1 sends it to 2, etc. When processor 0 receives the message, the program terminates. In the figure, only the branch office definition is listed. A Charm program has a main chare in which the execution starts. The branch office ring has

```

BranchOffice ring {

int next_node;

entry BranchInit : (message MSG *msg) {

RING_MSG *ring_msg;

next_node = (McMyPeNum() + 1) % McMaxPeNum();

if (McMyPeNum() == 0) {

ring_msg = (RING_MSG *) CkAllocMsg(RING_MSG);

SendMsgBranch(loop,ring_msg,next_node); }

}

entry loop : (message RING_MSG *msg) {

if (McMyPeNum() == 0) CkExit();

else SendMsgBranch(loop,msg,next_node);

}

```

Figure 2.13: A branch office - ring program.

two entries: BranchInit and loop. The BranchInit entry is the creation entry. That is, in some other part of the program, for example main, an instance of the ring is created by a CreateBoc call

```

ring_instance = CreateBoc(ring,ring@BranchInit,init_msg);

```

which returns a unique identifier for the instance of ring that has been just created. The creation process includes allocation of the local data structures of the branch chare and execution of the entry point specified in the CreateBoc call, BranchInit, on each processor.

In the ring example, when the BOC is created, only processor 0 sends a message to the branch of the same instance on the next processor (directed to the loop entry). Then the branch on processor 1 receives the message and passes it to processor 2, and this continues until processor 0 receives the message.

The Charm language has many system calls such as McMyPeNum(), CkAllocMsg etc. The list and details of these calls and other information can be found in the manual.

#### 2.5.1.4 Modules

One of the strong points of the Charm system is its support for developing modular message-driven programs. A Charm program file consists of a module, which contains names (definition) of messages, specifically shared variables, chares, branched chares, and C functions. These names are internal to the module. Some of these names can be made external and other modules can access these names. A name in another module is referred to by prefixing the name with the module name. For example, in order to access an entry point E of a chare C in a module M, the prefixed name would be M::CE.

Without entering in the details, we will give an example of multiple modules because it is relevant to our discussion in this section and in the following sections. A module uses an interface construct to declare its exported or imported names. Figure 2.14 shows an example interface construct. The module M2 imports some entities from the module M1 by including the interface file of M1 — M1.interface. The interface file defines the entities such as types, chares, and entry-points that are allowed to be accessed from other modules. In this example, M2 creates an instance of a chare, chare1, defined in M1 by accessing the chare name and entry point name, and message type. Similarly, other entities can be accessed.

#### 2.5.1.5 Other language features

In addition to messages, Charm provides other ways in which processes (chares and BOCs) share information. The discussion of these features is not closely relevant to the discussion here. The details about these mechanisms — namely, readonly, writeonce, monotonic variables, accumulators, and distributed tables — can be found in [16].

#### 2.5.2 The Charm runtime

The system keeps a pool of messages on each processor. These messages are either for creation of new objects (CreateChare) or for existing objects (SendMsg). Each message contains the instance of the chare and the entry point in addition to user data. On each processor, the runtime system repeatedly selects one of the available messages from the pool and executes the entry point code indicated by the message. This execution may change the state of the chare instance and may deposit new messages into the message pool. On a particular processor, an

```

#include ''M1.interface''

module M2 {

chare chare2 {

entry e2 : (message MSG2 *msg) {

m = (M1::MSG1 *) CkAllocMsg(M1::MSG1);

CreateChare(M1::chare1, M1::chare1e1,m);

}

}

}

(b)

interface module M1 {

message {int data;} MSG1;

chare chare1 {

entry e1 : (message MSG1 *msg) { }

}

}

```

Figure 2.14: Multiple modules in Charm (a) module M2 accesses entities in module M1 (b) interface module for M1 M1.interface.

entry point executes until completion and is not interrupted for activating another entry point code.

The message scheduling – selection of the messages from the pool – is done according to the scheduler. The system provides FIFO, LIFO, and priority-based scheduling policies, from which users can select one that suits their application. In addition, they can be substituted with other user supplied strategies.

## 2.6 Related work on latency tolerance

The idea of multiple contexts in which a processor switches between contexts in order to hide latencies is used at various levels in computer systems — from the language level to the architecture level. An early work in this area includes the future construct of [49]. A future is a process that can be executed in parallel with its parent process. When the parent needs the

value of the future, which is produced by the child, it blocks until the child has completed. This mechanism is analogous in some ways to SPMD style: if creation of a future is considered analogous to a request to some remote processor, then touching the future is equivalent to a blocking receive. This is not fully adaptive, because when waiting on multiple futures, the caller blocks for them in a fixed sequence. A future based system achives a degree of adaptive overlap, as multiple futures are assigned to the same processor concurrently assuming that a mechanism is provided for switching between them (by using threads, for instance).

The original Actor model as described in [1] is purely message driven. Actors are self-contained, interactive, independent components of a computation that communicate by asynchronous messages. Chares are similar to actors. One difference is that the methods of an actor can be executed concurrently (as defined in the Actor model), but the entry-points of a chare cannot be executed concurrently. One of the first implementations of the Actor model to run on parallel computers, HAL [56], was implemented on top of Charm. Other concurrent object oriented languages include ABCL/1 [6] and Concurrent Aggregates (CA) [17]. In ABCL/1, objects process one message at a time also, and objects can selectively receive messages. The CA language supports fine grain parallelism. An aggregate is a collection objects that has a single name. It supports concurrency within objects which can be distributed across processors. An object can create threads of computations by using the conc construct (similar to parbegin parend), and the variable synchronization is done by context futures.