# **Micro Channel Architecture**

| DescriptionMicro Channel ParticipantsAmastersSlavesSlavesMicro Channel StructureAddressing ModelMicro Channel Buses and SignalsArbitration Bus and Associated SignalsAddress Bus and Associated SignalsState of the sum of th |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Masters Slaves Micro Channel Structure Addressing Model  Micro Channel Buses and Signals Arbitration Bus and Associated Signals Address Bus and Associated Signals Address Signal Combinations Data Bus and Associated Signals Interrupt Signals Other Micro Channel Signals Channel Signal Groups (Digital) Matched-Memory Extension Signal Descriptions Auxiliary Video Extension Signal Descriptions Micro Channel Architecture Base and Extensions 32-Bit Connector and Extensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Slaves Micro Channel Structure Addressing Model  Micro Channel Buses and Signals Arbitration Bus and Associated Signals Address Bus and Associated Signals Address Signal Combinations Data Bus and Associated Signals Interrupt Signals Other Micro Channel Signals Channel Signal Groups (Digital) Matched-Memory Extension Signal Descriptions Auxiliary Video Extension Signal Descriptions 32-Bit Connector and Extensions 26 16-Bit Connector and Extensions 26 26 27 28 28 29 20 20 20 20 20 20 20 20 20 20 20 20 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Micro Channel Structure Addressing Model  Micro Channel Buses and Signals Arbitration Bus and Associated Signals Address Bus and Associated Signals Address Signal Combinations Data Bus and Associated Signals Interrupt Signals Interrupt Signals Other Micro Channel Signals Channel Signal Groups (Digital) Matched-Memory Extension Signal Descriptions Auxiliary Video Extension Signal Descriptions Auxiliary Video Extension Signal Descriptions 32-Bit Connector and Extensions 26 16-Bit Connector and Extensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Micro Channel Buses and Signals Arbitration Bus and Associated Signals Address Bus and Associated Signals Address Signal Combinations Data Bus and Associated Signals Interrupt Signals Other Micro Channel Signals Channel Signal Groups (Digital) Matched-Memory Extension Signal Descriptions Auxiliary Video Extension Signal Descriptions 32-Bit Connector and Extensions 16 17 18 19 10 10 11 12 13 14 15 16 16 16 17 17 17 17 17 17 17 17 17 17 17 17 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Arbitration Bus and Associated Signals Address Bus and Associated Signals Address Signal Combinations 12 Data Bus and Associated Signals Interrupt Signals Other Micro Channel Signals Channel Signal Groups (Digital) Matched-Memory Extension Signal Descriptions Auxiliary Video Extension Signal Descriptions Micro Channel Architecture Base and Extensions 32-Bit Connector and Extensions 16-Bit Connector and Extensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Arbitration Bus and Associated Signals Address Bus and Associated Signals Address Signal Combinations 12 Data Bus and Associated Signals Interrupt Signals Other Micro Channel Signals Channel Signal Groups (Digital) Matched-Memory Extension Signal Descriptions Auxiliary Video Extension Signal Descriptions Micro Channel Architecture Base and Extensions 32-Bit Connector and Extensions 16-Bit Connector and Extensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Address Bus and Associated Signals Address Signal Combinations Data Bus and Associated Signals Interrupt Signals Other Micro Channel Signals Channel Signal Groups (Digital) Matched-Memory Extension Signal Descriptions Auxiliary Video Extension Signal Descriptions Micro Channel Architecture Base and Extensions 32-Bit Connector and Extensions 26 16-Bit Connector and Extensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Address Signal Combinations 12 Data Bus and Associated Signals 13 Interrupt Signals 18 Other Micro Channel Signals 19 Channel Signal Groups (Digital) 20 Matched-Memory Extension Signal Descriptions 23 Auxiliary Video Extension Signal Descriptions 23 Micro Channel Architecture Base and Extensions 24 32-Bit Connector and Extensions 25 16-Bit Connector and Extensions 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Data Bus and Associated Signals13Interrupt Signals18Other Micro Channel Signals19Channel Signal Groups (Digital)20Matched-Memory Extension Signal Descriptions23Auxiliary Video Extension Signal Descriptions23Micro Channel Architecture Base and Extensions2432-Bit Connector and Extensions2516-Bit Connector and Extensions26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Interrupt Signals 18 Other Micro Channel Signals 19 Channel Signal Groups (Digital) 20 Matched-Memory Extension Signal Descriptions 23 Auxiliary Video Extension Signal Descriptions 23 Micro Channel Architecture Base and Extensions 24 32-Bit Connector and Extensions 25 16-Bit Connector and Extensions 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Other Micro Channel Signals       19         Channel Signal Groups (Digital)       20         Matched-Memory Extension Signal Descriptions       23         Auxiliary Video Extension Signal Descriptions       23         Micro Channel Architecture Base and Extensions       24         32-Bit Connector and Extensions       25         16-Bit Connector and Extensions       26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Channel Signal Groups (Digital)20Matched-Memory Extension Signal Descriptions23Auxiliary Video Extension Signal Descriptions23Micro Channel Architecture Base and Extensions2432-Bit Connector and Extensions2516-Bit Connector and Extensions26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Matched-Memory Extension Signal Descriptions23Auxiliary Video Extension Signal Descriptions23Micro Channel Architecture Base and Extensions2432-Bit Connector and Extensions2516-Bit Connector and Extensions26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

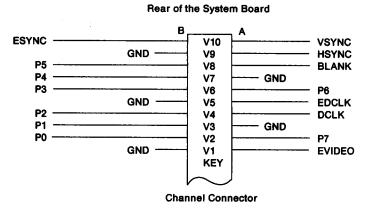

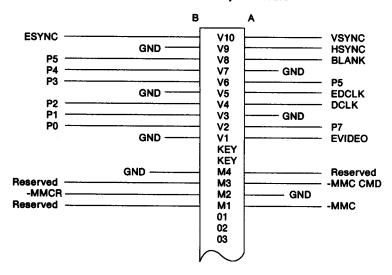

| Auxiliary Video Extension Signal Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

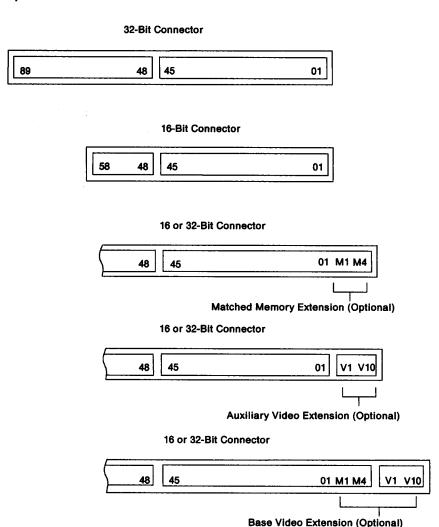

| Micro Channel Architecture Base and Extensions 24 32-Bit Connector and Extensions 25 16-Bit Connector and Extensions 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

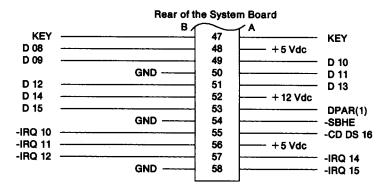

| 32-Bit Connector and Extensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

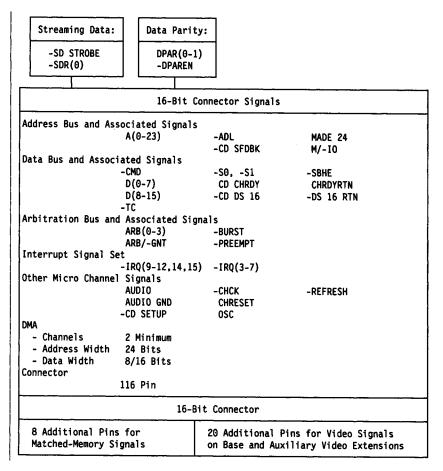

| 16-Bit Connector and Extensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Milera Obermal Duran June                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Micro Channel Procedures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

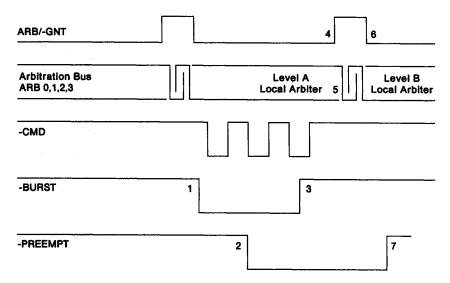

| Arbitration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Channel Ownership                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

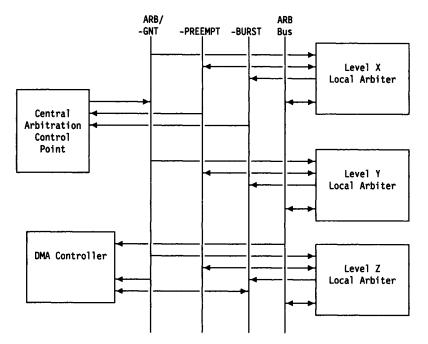

| Central Arbitration Control Point                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

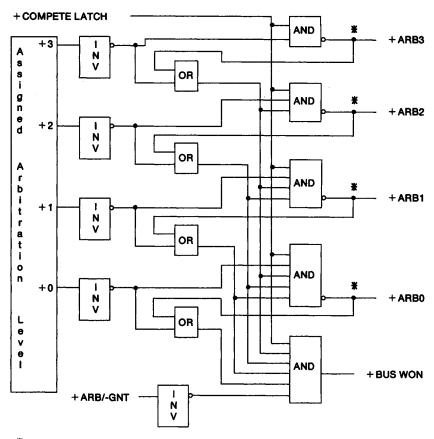

| Local Arbiters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Burst Transfer 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

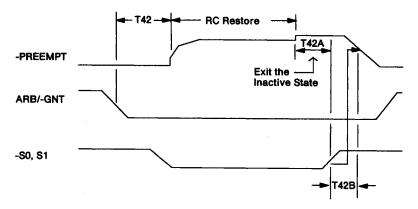

| Preemption 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Fairness Feature and the Inactive State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

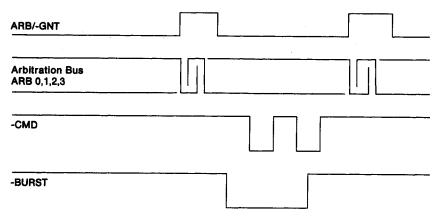

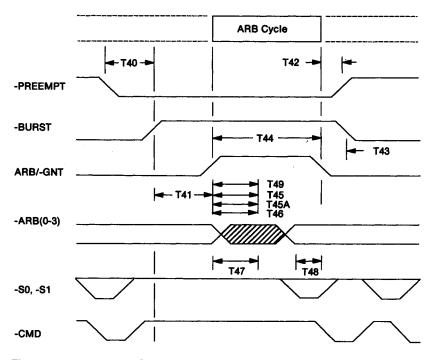

| Arbitration Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Data Transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

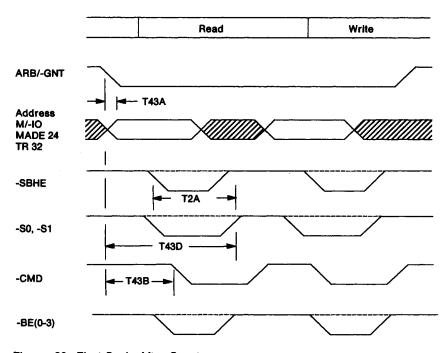

| Basic Transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Basic Transfer Procedure 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

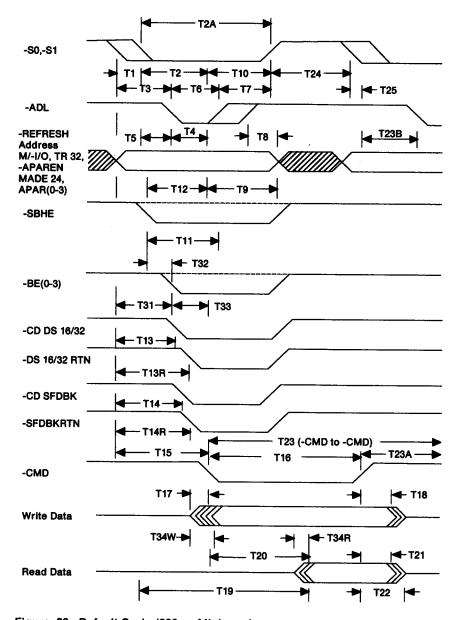

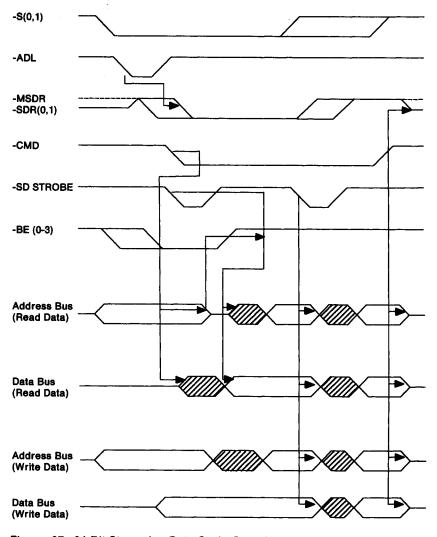

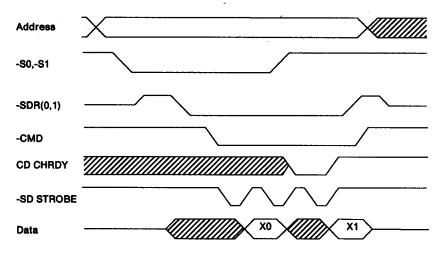

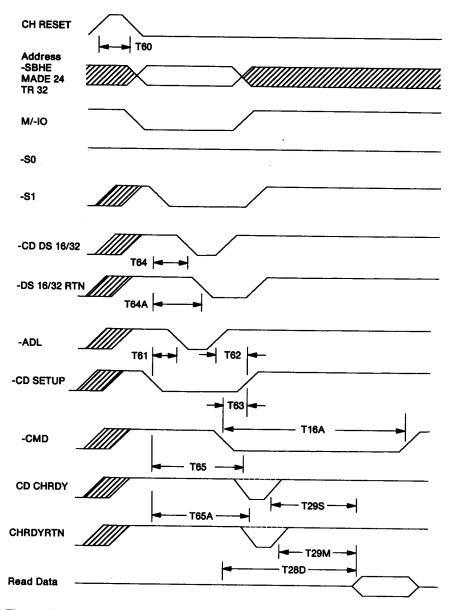

| Default Cycle Timing (200 ns Minimum)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

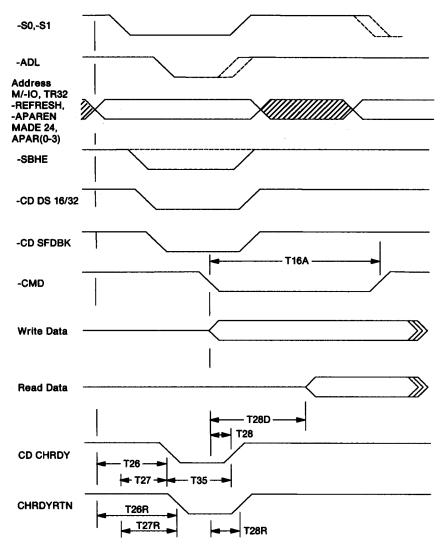

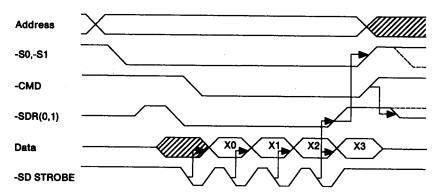

| Synchronous-Extended Cycle Timing (300 ns Minimum) 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

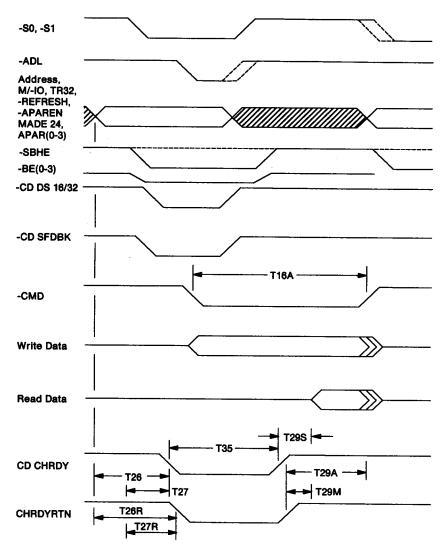

| Asynchronous-Extended Cycle Timing (≥300 ns)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

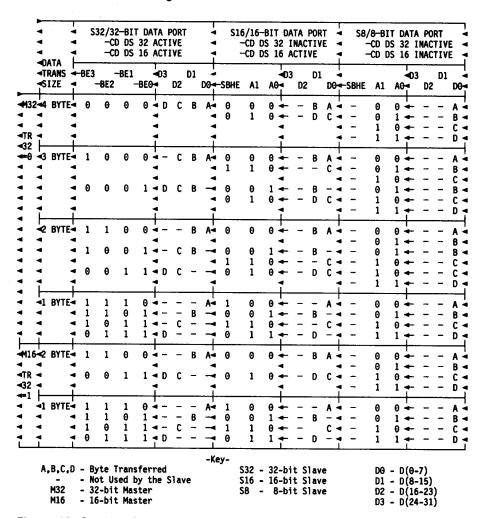

| Data Steering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Data Steering Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Master Replication of Data Bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Channel Support                                                   | 55  |

|-------------------------------------------------------------------|-----|

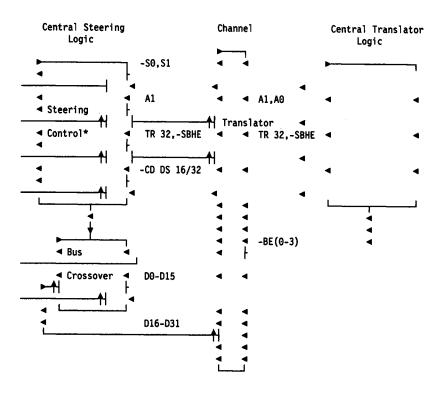

| Address Bus Translator                                            | 55  |

| Central Data Steering                                             | 56  |

| TR 32                                                             | 56  |

| Central Steering Logic                                            | 56  |

| Central Translator Logic                                          | 56  |

| -BE(0-3)                                                          | 56  |

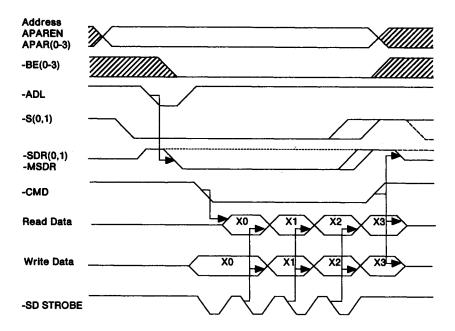

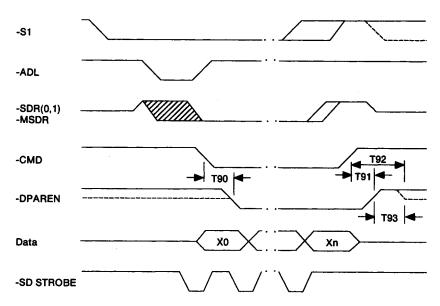

| Streaming Data Transfer                                           | 58  |

| Streaming Data Procedure (16- or 32-Bit)                          | 59  |

| Streaming Data Procedure (64-Bit)                                 | 61  |

| Streaming Data Transfer Rates                                     | 63  |

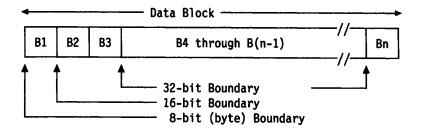

| Address Bus Management                                            | 63  |

| Address Boundary Alignment                                        | 64  |

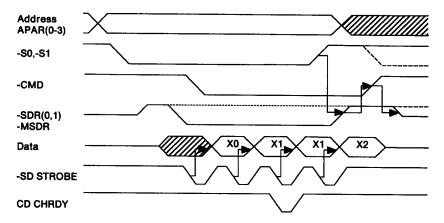

| Streaming Data Cycles                                             | 66  |

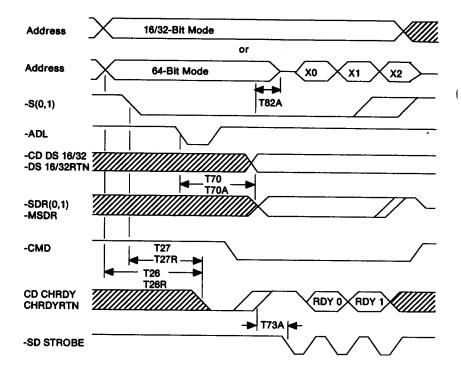

| 64-Bit Streaming Data Cycles                                      | 68  |

| Starting the Cycle                                                | 70  |

| Deferring the Start of the Cycle                                  | 70  |

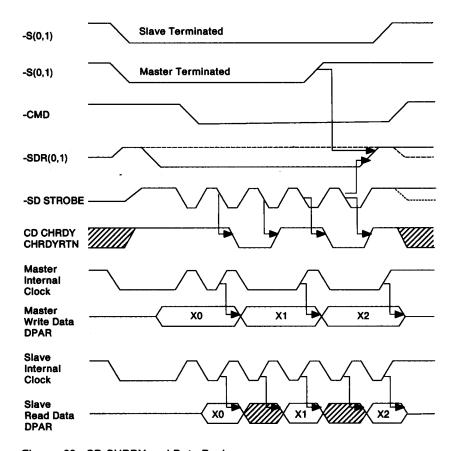

| Pacing the Data                                                   | 72  |

| Terminating the Cycle                                             | 74  |

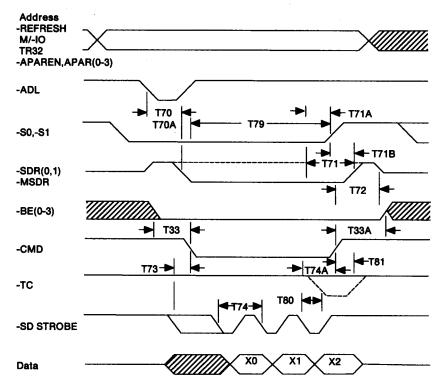

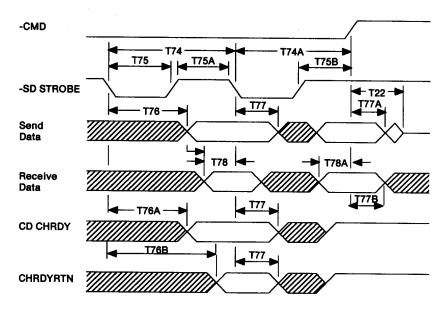

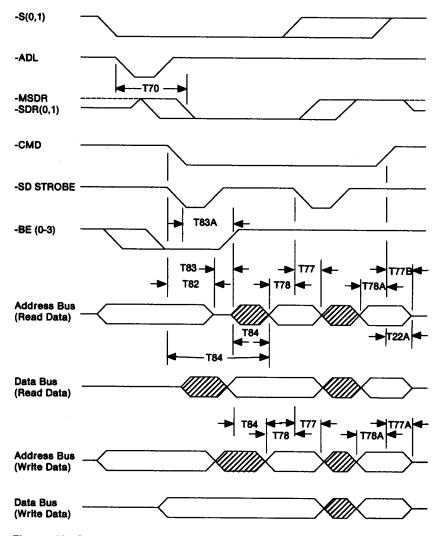

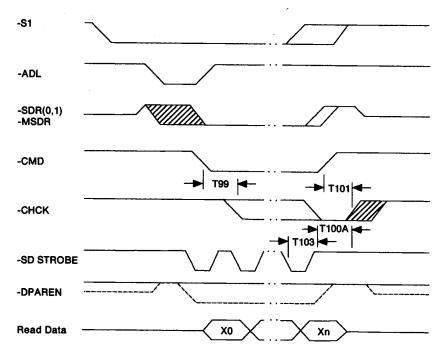

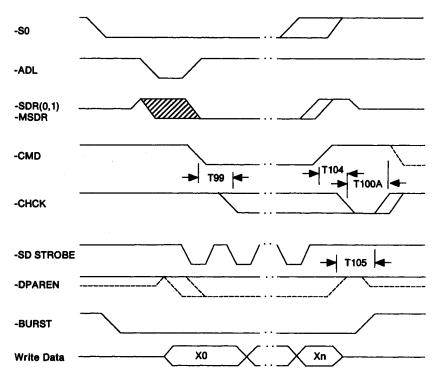

| Streaming Data Timing                                             | 77  |

| Direct Memory Access Procedure                                    | 83  |

| Read and Write Operations                                         | 83  |

| DMA Slave Selection                                               | 84  |

| Address During DMA Operation                                      | 84  |

| Transfer Data Length                                              | 84  |

| DMA Procedure                                                     | 84  |

| Single Transfer                                                   | 85  |

| Burst Transfer (Multiple Transfer Cycles)                         | 86  |

| DMA Terminating Conditions                                        | 86  |

| Use of -BURST                                                     | 87  |

| DMA Timings                                                       | 88  |

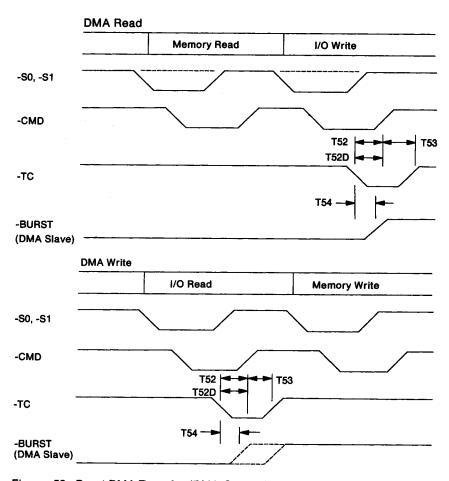

| Single DMA Transfer (DMA-Controller Controlled)                   | 88  |

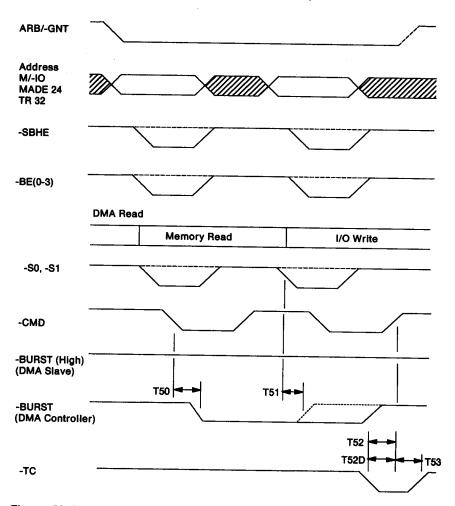

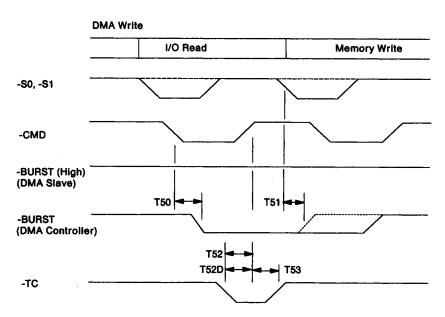

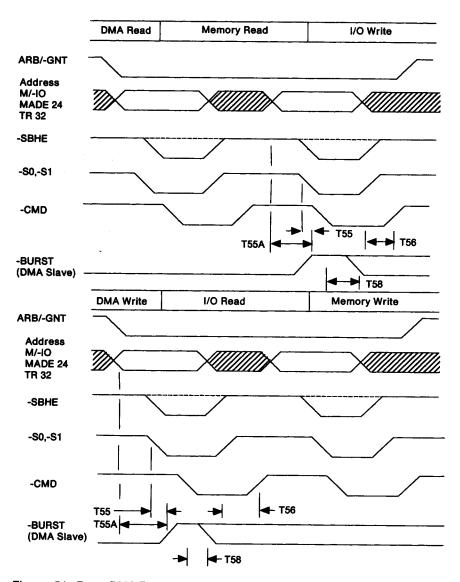

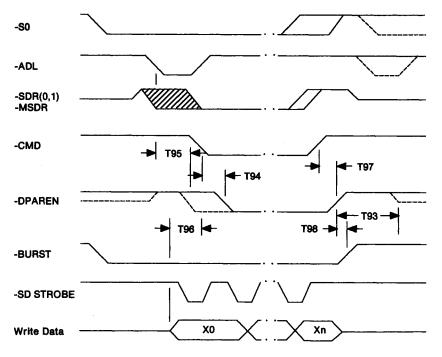

| Burst DMA Transfer (DMA-Controller Terminated)                    | 90  |

| Burst DMA Transfer (DMA-Slave Terminated - Default Cycle, 200 ns) |     |

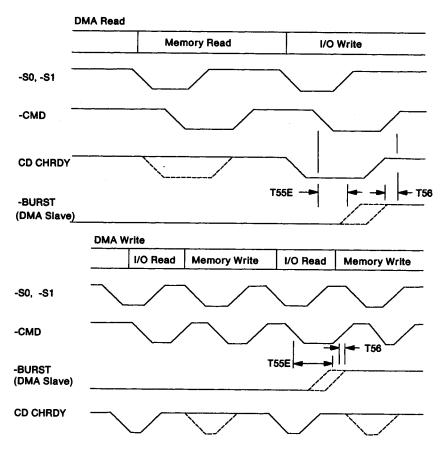

| Burst DMA Transfer (DMA-Slave Terminated -                        | 91  |

| Synchronous-Extended Cycle, 300 ns)                               | 94  |

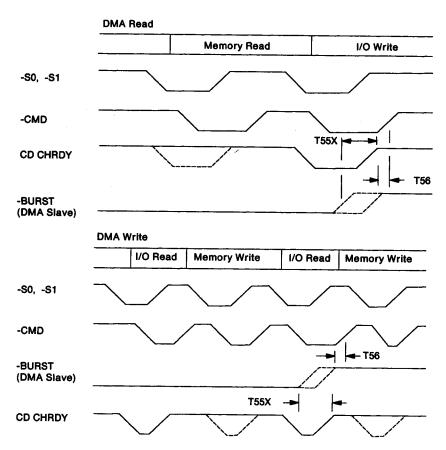

| Burst DMA Transfer (DMA Slave Terminated -                        | 34  |

| Asynchronous-Extended Cycle, ≥300 ns)                             | 96  |

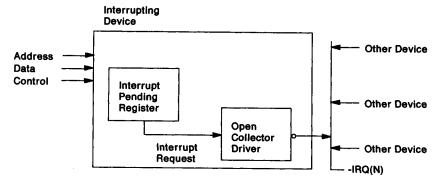

| Interrupt Procedures                                              | 98  |

| Refresh                                                           | 100 |

| System Configuration                                              | 100 |

| Multiple Card Adapters                                            | 101 |

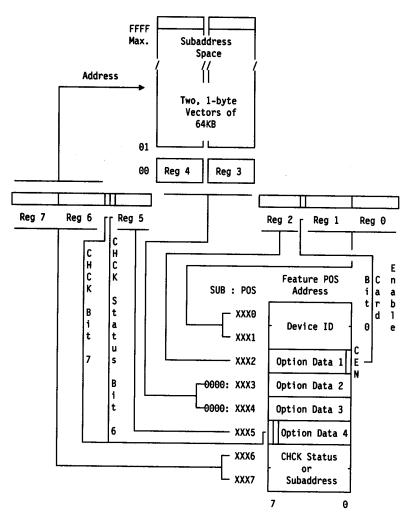

| Adapter Configuration Data                      | 103 |

|-------------------------------------------------|-----|

| Required Configuration Fields                   | 103 |

| Adapter ID Field                                | 104 |

| Card Enable Field                               | 104 |

| Channel Check Field                             | 104 |

| Conditionally-Required Configuration Fields     | 104 |

| Adapter I/O Address Select Field                | 105 |

| Adapter ROM/RAM Address Select Field            | 105 |

| Arbitration Level Field                         | 105 |

| Auto-Incrementing Enable Field                  | 105 |

| Channel Check Exception Reporting Field         | 106 |

| Channel Check Status Indicator Field            | 106 |

| Data and Address Parity Enable Field            | 106 |

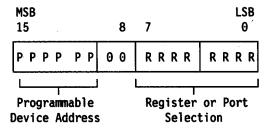

| Device I/O Address Assignment                   | 106 |

| Matched Memory Enable Field                     | 107 |

| Selected Feedback Return Exception Enable Field | 107 |

| Streaming Data Enable Field                     | 108 |

| Optional Configuration Fields                   | 108 |

| Option Select Data Field                        | 108 |

| Fairness Feature Enable Field                   | 108 |

| POS Subaddress Extension Field                  | 108 |

| Status Information Field                        | 111 |

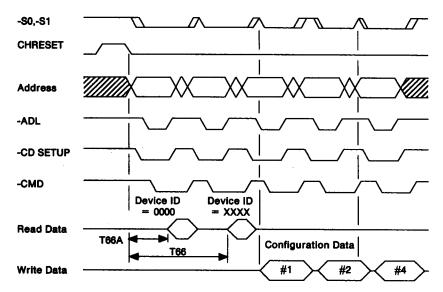

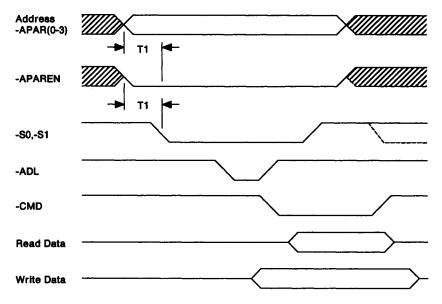

| System Configuration Procedure                  | 112 |

| Address Bus During Setup Cycles                 | 112 |

| Card Enable Field During Setup Cycles           | 113 |

| Channel Check Status During Setup Cycles        | 113 |

| -CD SETUP During Setup Cycles                   | 113 |

| CD CHRDY During Setup Cycles                    | 113 |

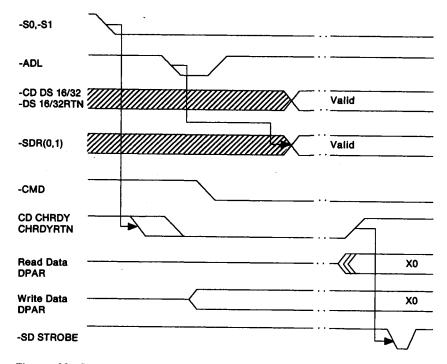

| System Configuration Timing Diagrams            | 114 |

| Exception Condition Reporting and Handling      | 118 |

| Exception Conditions                            | 118 |

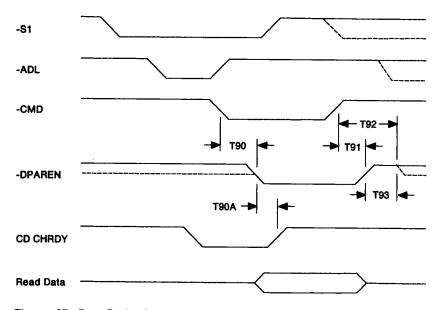

| Channel Data and Address Parity Exceptions      | 119 |

| Data Parity                                     | 120 |

| Read Operations - Basic Transfer                | 120 |

| Read Operations - Streaming Data Transfer       | 122 |

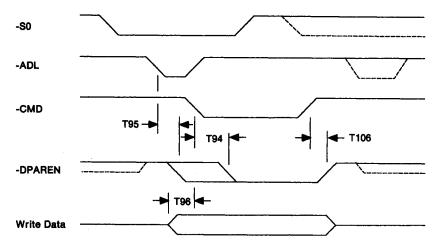

| Write Operations - Basic Transfer               | 122 |

| Write Operations - Streaming Data Transfer      | 124 |

| Data Parity Exception Handling                  | 126 |

| Bus Master                                      | 126 |

| System Master                                   | 126 |

| DMA Controller                                  | 126 |

| Slaves                                          | 126 |

| Address Parity                                  | 127 |

| Channel Non-Parity Exceptions                     |

|---------------------------------------------------|

| Invalid -DS 16 RTN and -DS 32 RTN Combination 128 |

| Selected Feedback Return Exception 129            |

| Master and Slave Dependent Exceptions 130         |

| Channel Timeout Exception                         |

| Exception Reporting                               |

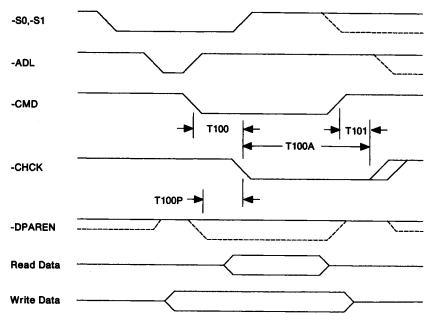

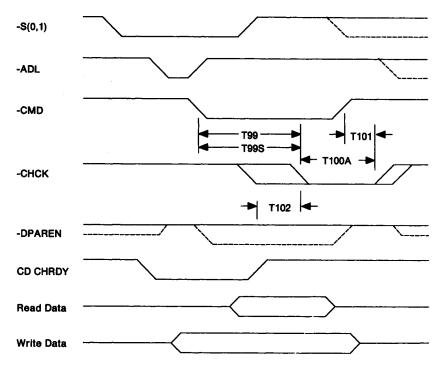

| Exception Reporting using -CHCK                   |

| Synchronous -CHCK                                 |

| Asynchronous -CHCK                                |

| Exception Reporting Using Interrupts              |

| Exception Handling 138                            |