# Performance and Tuning **Considerations for the** p690 in a Cluster 1600

## IBM

## International Technical Support Organization

# Performance and Tuning Considerations for the p690 in a Cluster 1600

August 2002

| <b>Note:</b> Before using this information and the product it supports, read the information in "Notices" on page xi.                                |

|------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                      |

|                                                                                                                                                      |

|                                                                                                                                                      |

|                                                                                                                                                      |

|                                                                                                                                                      |

|                                                                                                                                                      |

|                                                                                                                                                      |

|                                                                                                                                                      |

|                                                                                                                                                      |

|                                                                                                                                                      |

|                                                                                                                                                      |

|                                                                                                                                                      |

|                                                                                                                                                      |

|                                                                                                                                                      |

|                                                                                                                                                      |

|                                                                                                                                                      |

|                                                                                                                                                      |

|                                                                                                                                                      |

|                                                                                                                                                      |

|                                                                                                                                                      |

|                                                                                                                                                      |

| First Edition (August 2002)                                                                                                                          |

| This edition applies to Version 3, Release 4, of IBM Parallel System Support Program, for use with the IBM AIX Operating System Version 5 Release 1. |

© Copyright International Business Machines Corporation 2002. All rights reserved.

Note to U.S. Government Users Restricted Rights -- Use, duplication or disclosure restricted by GSA ADP Schedule Contract with IBM Corp.

## **Contents**

| Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | vi                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ix                                           |

| Notices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                              |

| Preface The team that wrote this redbook.  Become a published author  Comments welcome.                                                                                                                                                                                                                                                                                                                                                                                                | xii<br>xv                                    |

| Chapter 1. Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1                                            |

| Chapter 2. Hardware overview  2.1 What is a Cluster 1600  2.2 The pSeries 690 POWER4 building blocks  2.2.1 The processor subsystem  2.2.2 The memory subsystem  2.2.3 The input/output (I/O) subsystem  2.3 The interconnect fabric  2.3.1 The SP Switch2.  2.3.2 The SP Switch2 PCI Attachment Adapter.  2.3.3 Internet Protocol (IP) and User Space (US) windows  2.4 Summary.                                                                                                      | 7 9 12 17 20 27 29 32                        |

| Chapter 3. Features relevant to performance  3.1 Logical partitions (LPARs).  3.1.1 The Hypervisor  3.1.2 LPAR memory overhead.  3.1.3 LPAR mode versus Full System Partition mode.  3.1.4 LPAR memory and processor allocation.  3.2 Affinity logical partitions (ALPARs).  3.3 Technical large page support.  3.3.1 Technical large pages and the Virtual Memory Manager (VMM).  3.3.2 Technical large page usage.  3.4 Memory affinity.  3.4.1 Memory configuration of pSeries 690. | 36<br>38<br>40<br>42<br>44<br>45<br>47<br>52 |

| 3.4.2 Enabling memory affinity                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 54                                           |

| 3.4.3 Performance considerations for memory affinity              | 55  |

|-------------------------------------------------------------------|-----|

| 3.4.4 Memory affinity with technical large page support           |     |

| 3.5 The 32-bit kernel versus the 64-bit kernel                    |     |

| 3.5.1 Selecting the 64-bit kernel                                 |     |

| 3.5.2 The 64-bit application environment                          |     |

| 3.6 Application performance tuning                                |     |

| 3.6.1 Application tuning guidelines and resources                 |     |

| 3.6.2 Compiler considerations                                     |     |

| 3.6.3 Engineering and Scientific Subroutine Libraries             |     |

| 3.6.4 The Mathematical Acceleration Subsystem (MASS) library      |     |

| 3.6.5 Hostfile considerations for MPI performance                 |     |

| 3.6.6 Some final recommendations                                  |     |

| 3.7 Network connectivity                                          |     |

| 3.7.1 SP Switch2 PCI Attachment Adapter                           |     |

| 3.7.2 EtherChannel configurations                                 |     |

| 3.7.3 Internet Protocol (IP) and User Space (US) switch windows   |     |

| 3.8 What is next                                                  |     |

|                                                                   |     |

| Chapter 4. Investigations                                         |     |

| 4.1 Technical large page investigation                            |     |

| 4.1.1 Setting up the environment for technical large page         |     |

| 4.1.2 Creating the Melville MD10 dataset for technical large page |     |

| 4.1.3 Running the tests for technical large page                  |     |

| 4.1.4 Conclusions from the first attempt at technical large page  |     |

| 4.1.5 The second attempt at technical large page                  |     |

| 4.1.6 Running both tests again within an affinity LPAR (ALPAR)    |     |

| 4.1.7 Three steps forward, one step back                          |     |

| 4.1.8 Memory affinity                                             |     |

| 4.1.9 Technical large page investigation conclusions              |     |

| 4.2 Tivoli Storage Manager (TSM) investigations                   |     |

| 4.2.1 TSM environment without large page                          |     |

| 4.2.2 TSM environment with technical large page                   |     |

| 4.2.3 TSM and technical large page conclusions                    |     |

| 4.2.4 TSM and SP Switch2 communication                            |     |

| 4.2.5 TSM and SP Switch2 conclusions                              |     |

| 4.3 IP vs. US investigation                                       |     |

| 4.3.1 Setting up the environment for IP vs. US testing            |     |

| 4.3.2 Running the tests for IP vs. US                             |     |

| 4.3.3 IP vs. US on larger LPARs                                   |     |

| 4.3.4 IP vs. US with different hostfile                           |     |

| 4.3.5 IP vs. US with MP_SHARED_MEMORY=yes                         |     |

| 4.3.6 IP vs. US with single LPAR using shared memory              |     |

| 4.3.7 IP vs. US investigation conclusions                         | 128 |

| 4.4 CHARMm IP vs. US investigation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.4.1 Setting up the environment for IP vs. US testing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4.4.2 Running the tests for IP vs. US                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 4.4.3 CHARMm IP vs. US investigation conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| <b>Chapter 5. Summary</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Appendix A. Scripts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| The pmrinfo tool                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| The mkllqwcoll tool                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| The fix_nlspath tool                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| The mk_temp_dir                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| The rm_temp_dir                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Appendix B. MPI sample programs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| The inverse_parallel_enabled.c MPI program                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| The inverse_parallel.c MPI program164                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| The series_parallel.c MPI program                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Appendix C. Parallel tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| PE Benchmarker                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| MPI Trace                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Appendix D. Integrating p690 in an IBM eServer Cluster 1600 183                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Appendix D. Integrating p690 in an IBM eServer Cluster 1600                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Appendix D. Integrating p690 in an IBM eServer Cluster 1600                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Appendix D. Integrating p690 in an IBM eServer Cluster 1600                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

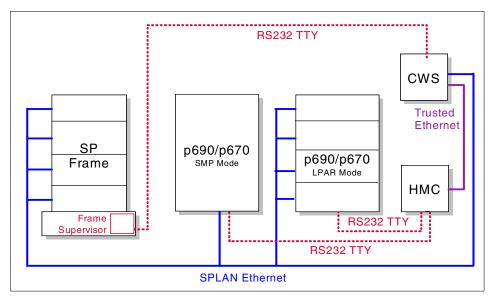

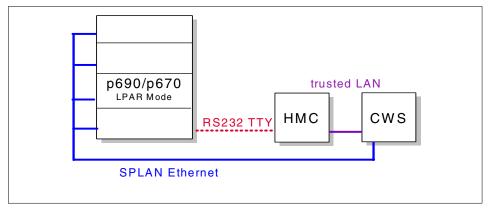

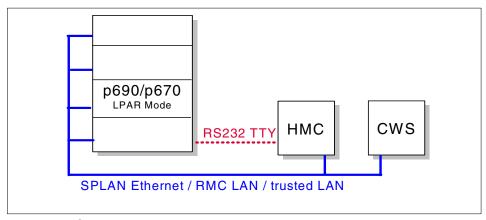

| Appendix D. Integrating p690 in an IBM eServer Cluster 1600       183         IBM eServer pSeries 690       184         What is an LPAR       184         What is an HMC       185         IBM eServer p690 in a Cluster       185         CWS, HMC, and p690 functions       186                                                                                                                                                                                                                                                                                                                                 |

| Appendix D. Integrating p690 in an IBM eServer Cluster 1600       183         IBM eServer pSeries 690       184         What is an LPAR       184         What is an HMC       185         IBM eServer p690 in a Cluster       185         CWS, HMC, and p690 functions       186         The role of the CWS for an attached p690 server       186                                                                                                                                                                                                                                                               |

| Appendix D. Integrating p690 in an IBM eServer Cluster 1600       183         IBM eServer pSeries 690       184         What is an LPAR       184         What is an HMC       185         IBM eServer p690 in a Cluster       185         CWS, HMC, and p690 functions       186         The role of the CWS for an attached p690 server       186         The role of the HMC in a Cluster 1600       187                                                                                                                                                                                                       |

| Appendix D. Integrating p690 in an IBM eServer Cluster 1600       183         IBM eServer pSeries 690       184         What is an LPAR       184         What is an HMC       185         IBM eServer p690 in a Cluster       185         CWS, HMC, and p690 functions       186         The role of the CWS for an attached p690 server       186         The role of the HMC in a Cluster 1600       187         Connectivity between CWS, HMC, and p690       187                                                                                                                                             |

| Appendix D. Integrating p690 in an IBM eServer Cluster 1600                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Appendix D. Integrating p690 in an IBM eServer Cluster 1600 183  IBM eServer pSeries 690 184  What is an LPAR 185  What is an HMC 185  IBM eServer p690 in a Cluster 185  CWS, HMC, and p690 functions 186  The role of the CWS for an attached p690 server 186  The role of the HMC in a Cluster 1600 187  Connectivity between CWS, HMC, and p690 187  Mapping LPAR numbers and node numbers 190  Planning considerations 193                                                                                                                                                                                   |

| Appendix D. Integrating p690 in an IBM eServer Cluster 1600 183 IBM eServer pSeries 690 184 What is an LPAR 185 What is an HMC 185 IBM eServer p690 in a Cluster 185 CWS, HMC, and p690 functions 186 The role of the CWS for an attached p690 server 186 The role of the HMC in a Cluster 1600 187 Connectivity between CWS, HMC, and p690 187 Mapping LPAR numbers and node numbers 190 Planning considerations 193 Control workstation 193                                                                                                                                                                     |

| Appendix D. Integrating p690 in an IBM eServer Cluster 1600 1830 IBM eServer pSeries 690 1840 What is an LPAR 1840 What is an HMC 1850 IBM eServer p690 in a Cluster 1850 CWS, HMC, and p690 functions 1850 The role of the CWS for an attached p690 server 1850 The role of the HMC in a Cluster 1600 1870 Connectivity between CWS, HMC, and p690 1870 Mapping LPAR numbers and node numbers 1950 Planning considerations 1950 Control workstation 1950 Hardware Management Console 1950                                                                                                                        |

| Appendix D. Integrating p690 in an IBM eServer Cluster 1600                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Appendix D. Integrating p690 in an IBM eServer Cluster 1600                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Appendix D. Integrating p690 in an IBM eServer Cluster 1600                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Appendix D. Integrating p690 in an IBM eServer Cluster 1600 183 IBM eServer pSeries 690 184 What is an LPAR 185 What is an HMC 185 IBM eServer p690 in a Cluster 185 CWS, HMC, and p690 functions 186 The role of the CWS for an attached p690 server 186 The role of the HMC in a Cluster 1600 187 Connectivity between CWS, HMC, and p690 187 Mapping LPAR numbers and node numbers 190 Planning considerations 193 Control workstation 193 Hardware Management Console 195 IBM eServer p690 195 Prepare the Hardware Management Console 197 Software levels 197 Serial connection 197                          |

| Appendix D. Integrating p690 in an IBM eServer Cluster 1600 183 IBM eServer pSeries 690 184 What is an LPAR 185 What is an HMC 185 IBM eServer p690 in a Cluster 185 CWS, HMC, and p690 functions 186 The role of the CWS for an attached p690 server 186 The role of the HMC in a Cluster 1600 187 Connectivity between CWS, HMC, and p690 187 Mapping LPAR numbers and node numbers 190 Planning considerations 193 Control workstation 193 Hardware Management Console 195 IBM eServer p690 195 Prepare the Hardware Management Console 197 Software levels 197 Serial connection 197 System configuration 198 |

| Appendix D. Integrating p690 in an IBM eServer Cluster 1600 183 IBM eServer pSeries 690 184 What is an LPAR 185 What is an HMC 185 IBM eServer p690 in a Cluster 185 CWS, HMC, and p690 functions 186 The role of the CWS for an attached p690 server 186 The role of the HMC in a Cluster 1600 187 Connectivity between CWS, HMC, and p690 187 Mapping LPAR numbers and node numbers 190 Planning considerations 193 Control workstation 193 Hardware Management Console 195 IBM eServer p690 195 Serial connection 197 System configuration 196 Security settings 196                                           |

| Appendix D. Integrating p690 in an IBM eServer Cluster 1600 183 IBM eServer pSeries 690 184 What is an LPAR 185 What is an HMC 185 IBM eServer p690 in a Cluster 185 CWS, HMC, and p690 functions 186 The role of the CWS for an attached p690 server 186 The role of the HMC in a Cluster 1600 187 Connectivity between CWS, HMC, and p690 187 Mapping LPAR numbers and node numbers 190 Planning considerations 193 Control workstation 193 Hardware Management Console 195 IBM eServer p690 195 Prepare the Hardware Management Console 197 Software levels 197 Serial connection 197 System configuration 198 |

| Required p690 firmware                                 |       |

|--------------------------------------------------------|-------|

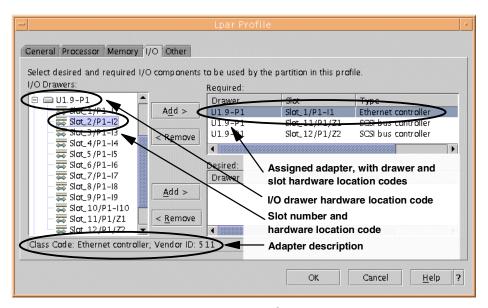

| Adapter placement for p690                             |       |

| Prepare the control workstation                        | . 206 |

| AIX and PSSP software requirements                     |       |

| Software coexistence                                   | . 208 |

| Accessing the Hardware Management Console              |       |

| Set hardmon authentication                             | . 211 |

| Define switch node numbers                             |       |

| PSSP changes                                           |       |

| Hardware monitoring                                    | . 213 |

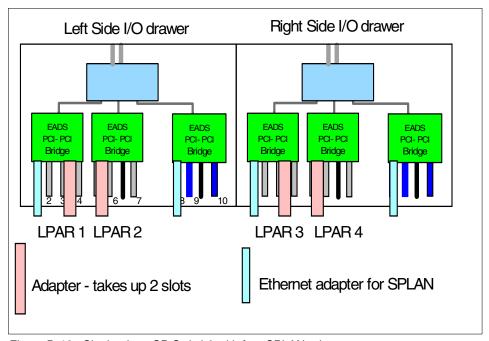

| SPLAN adapter                                          | . 217 |

| Additional SDR information                             | . 219 |

| Perspectives                                           |       |

| New commands and new command flags                     | . 223 |

| Configuring p690                                       | . 229 |

| Adding p690 to a Cluster                               |       |

| Adding p690 LPARs to a Cluster                         | . 230 |

| Deleting LPARs in a Cluster                            | . 231 |

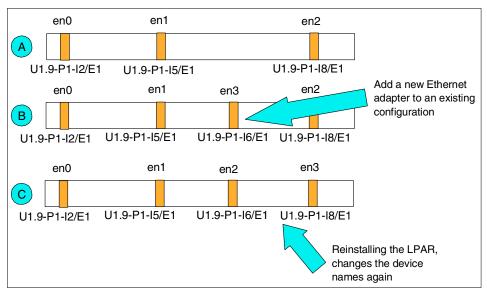

| Adding an Ethernet adapter to an LPAR node             | . 232 |

| Reconfiguring LPARs                                    |       |

| Node numbering                                         |       |

| Move or replace the SPLAN adapter                      |       |

| Using multiple LPAR definitions or profiles            |       |

| Switching between LPAR and Full System Partition mode  |       |

| Helpful feature codes                                  |       |

| Limitations                                            |       |

| Example scenarios                                      |       |

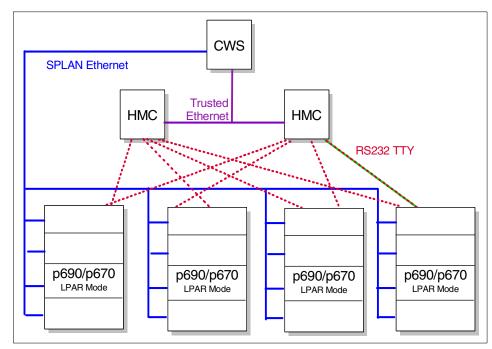

| CWS with two HMCs and four p690s                       |       |

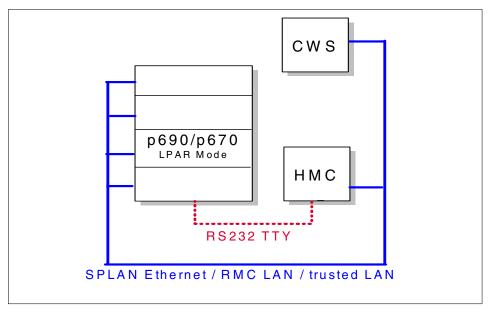

| One CWS, one HMC, and one p690                         |       |

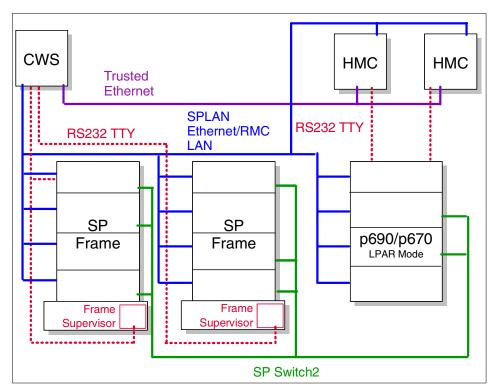

| CWS, two HMCs, two 9076s, with one p690 and SP Switch2 |       |

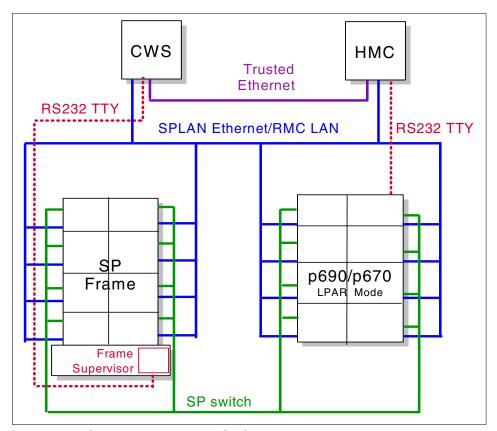

| CWS, HMC, 9076 frame, and p690 with SP Switch          |       |

| •                                                      |       |

| Related publications                                   |       |

| IBM Redbooks                                           |       |

| Other resources                                        |       |

| Referenced Web sites                                   | . 247 |

| How to get IBM Redbooks                                |       |

| IBM Redbooks collections                               | . 248 |

| Abbreviations and acronyms                             | . 249 |

|                                                        |       |

| In day                                                 | OFO   |

## **Figures**

| 2-1  | The pSeries 690 architecture                                         | 11    |

|------|----------------------------------------------------------------------|-------|

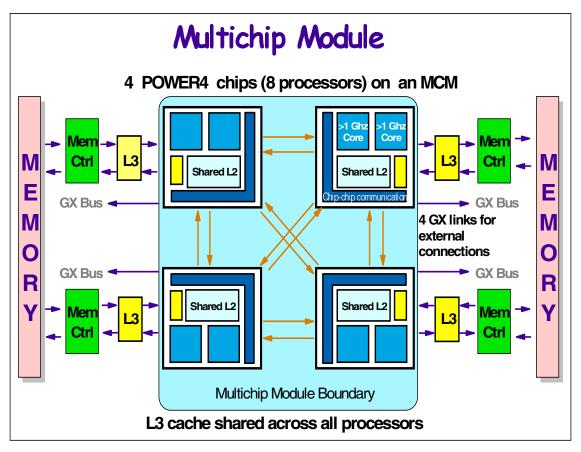

| 2-2  | The pSeries 690 Multi-Chip Module (MCM)                              | 13    |

| 2-3  | pSeries 690 fully-populated CEC                                      | 14    |

| 2-4  | Inside the POWER4 chip                                               |       |

| 2-5  | Logical view of POWER4 memory                                        | 19    |

| 2-6  | The many stages of the RIO subsystem                                 | 24    |

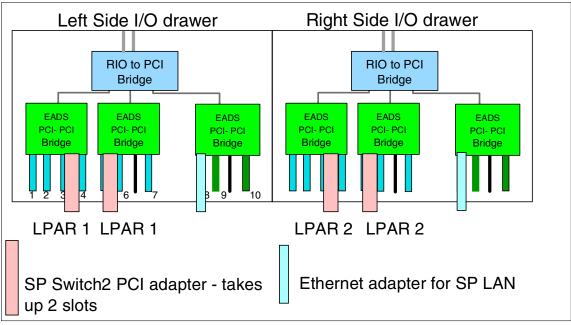

| 2-7  | SP Switch2 PCI Attachment Adapter location for a single plane switch | h 31  |

| 2-8  | SP Switch2 PCI Attachment Adapter location for dual plane switch .   | 32    |

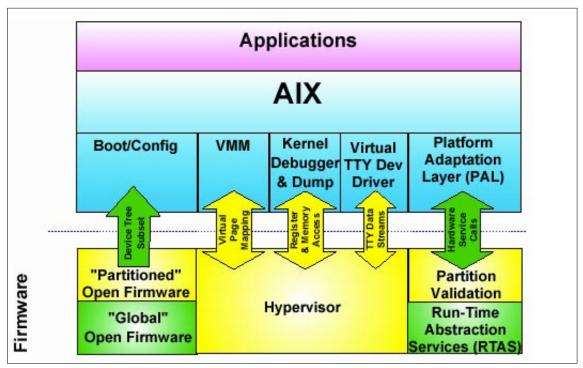

| 3-1  | The POWER4 Hypervisor                                                | 37    |

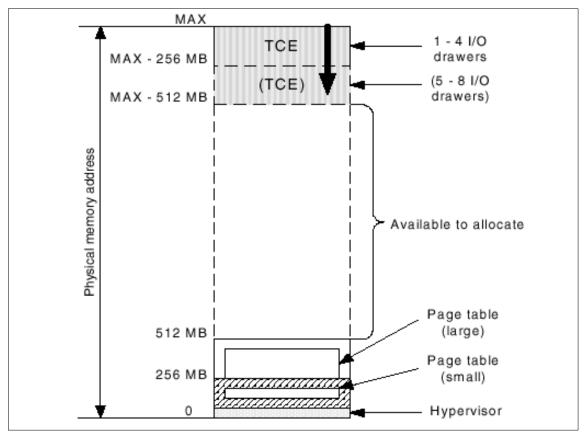

| 3-2  | Reserved memory in an LPAR environment                               | 39    |

| 3-3  | Logical view of MCM and memory                                       | 53    |

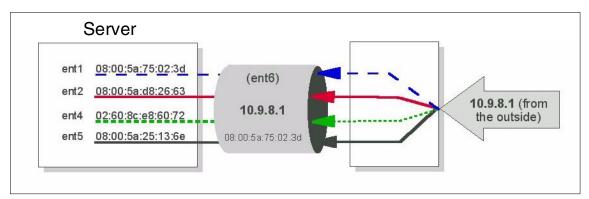

| 3-4  | Four-link EtherChannel schema                                        | 73    |

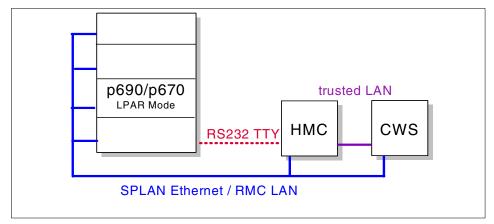

| D-1  | p690 attachment in a Cluster                                         | . 186 |

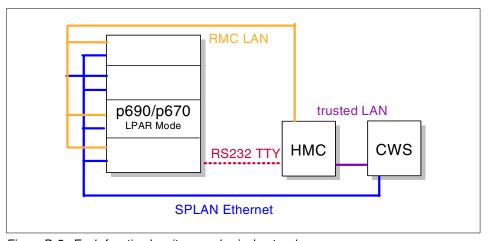

| D-2  | The RMC LAN uses the SPLAN and the trusted network                   | . 189 |

| D-3  | Cluster with only one physical network                               | . 189 |

| D-4  | Cluster with two physical networks                                   |       |

| D-5  | Each function has its own physical network                           |       |

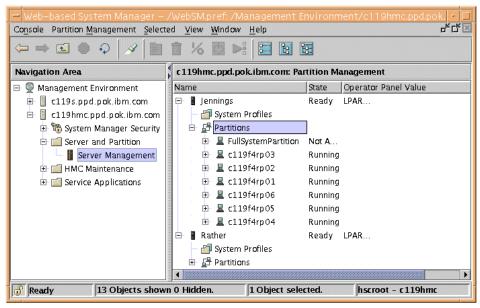

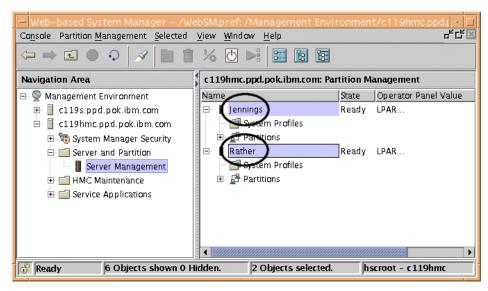

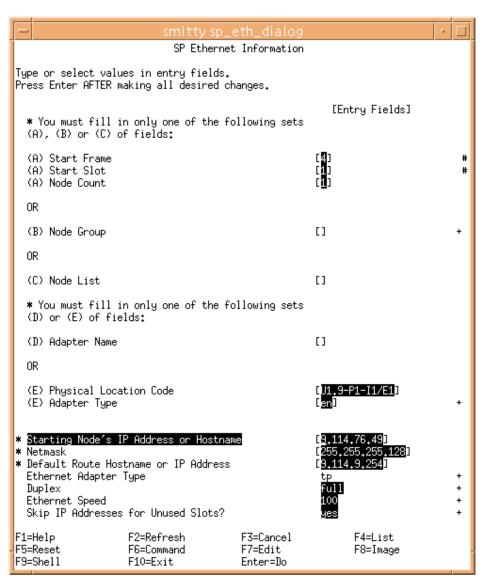

| D-6  | Screen shot of the HMC where you find the LPAR names                 |       |

| D-7  | Example node numbering in frames (9076 and p690)                     |       |

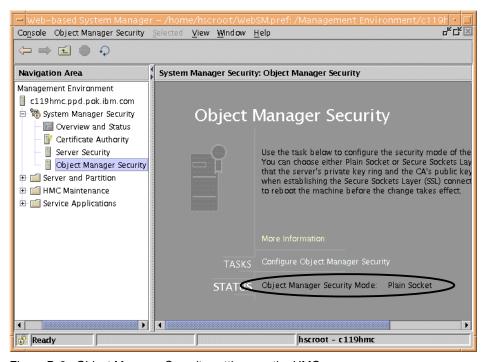

| D-8  | Object Manager Security settings on the HMC                          |       |

| D-9  | HMC WebSM interface with configured p690 domain names                |       |

| D-10 | The opened vterm session to the p690 service processor               |       |

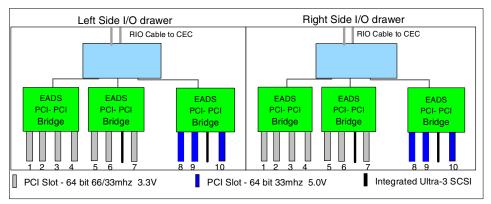

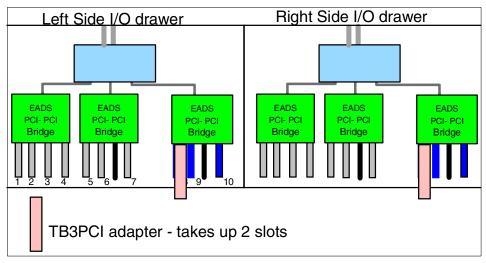

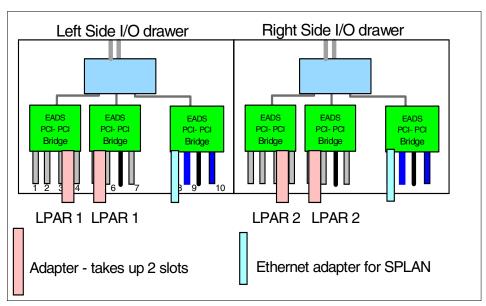

| D-11 | Logical view (rear view) of an I/O adapter drawer of a p690          | . 203 |

| D-12 | I/O adapter drawer with two SP Switch adapters                       |       |

| D-13 | Single-plane SP Switch2 with four SPLAN adapters                     |       |

| D-14 | Dual-plane SP Switch2 with two SPLAN adapters                        |       |

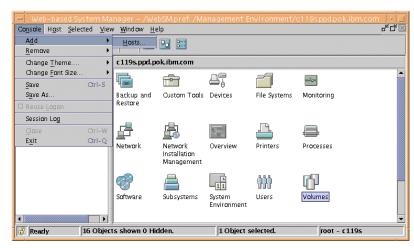

| D-15 | Add host to WebSM interface                                          |       |

| D-16 | Setting HMC user name and password                                   |       |

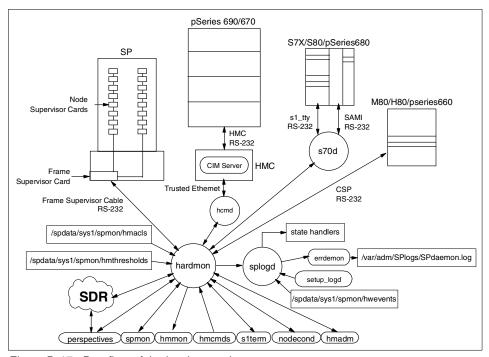

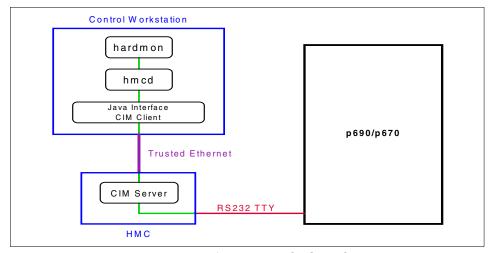

| D-17 | Dataflow of the hardmon subsystem                                    |       |

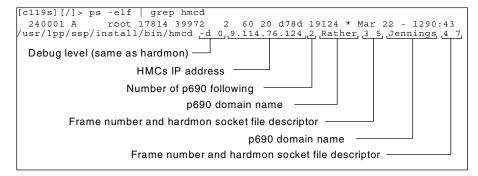

| D-18 | ps command output of a running hmcd daemon                           |       |

| D-19 | hardmon and hmcd dataflow between CWS, HMC, and p690                 |       |

| D-20 | Physical location codes and logical AIX device names                 |       |

| D-21 | Hardware location codes on the HMC                                   |       |

| D-22 | The spled window with two attached p690 servers                      |       |

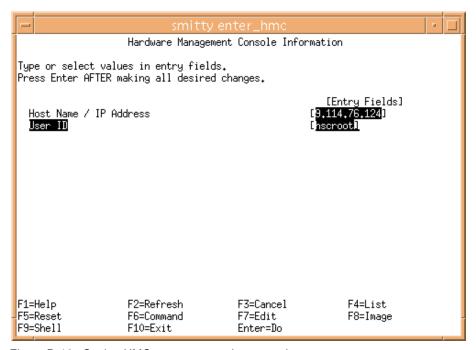

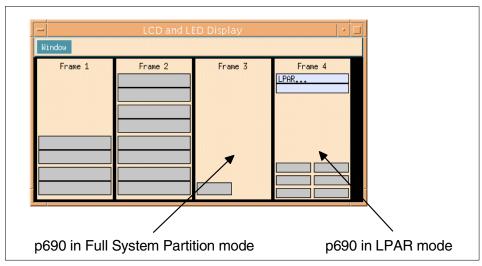

| D-23 | SMIT hmc_frame_dialog screen shot                                    |       |

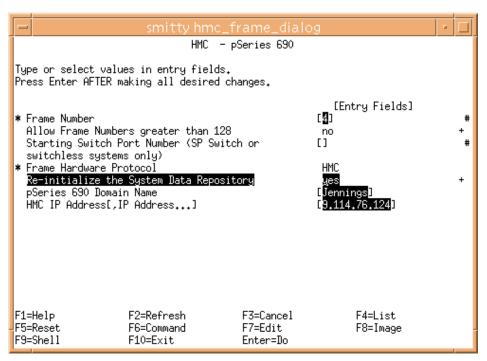

| D-24 | SMIT sp_eth_dialog screen shot                                       |       |

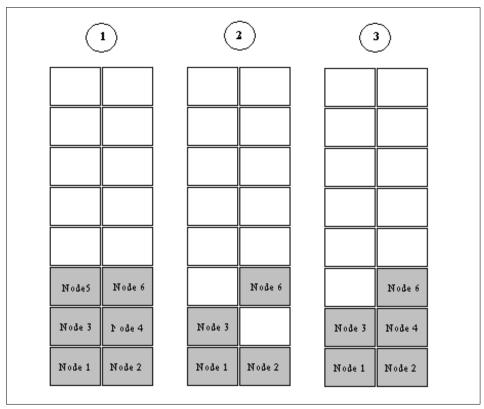

| D-25 | Node numbers when reconfiguring LPARs                                |       |

| D-26 | Four p690s with two redundant HMCs and one CWS                       | . 240 |

| D-27 | Cluster 1600 with one HMC, one p690, and CWS           | . 241 |

|------|--------------------------------------------------------|-------|

| D-28 | SP Frames with one p690 and two LPARs on an SP Switch2 | . 242 |

| D-29 | SP Frame and p690 with SP-Switched LPARs               | . 243 |

## **Tables**

| 1-1  | Other related IBM publications                                 | 2   |

|------|----------------------------------------------------------------|-----|

| 2-1  | Cluster 1600 node building blocks                              | 7   |

| 2-2  | Interconnect hardware latency and peak bandwidth               | 8   |

| 2-3  | Mapping of POWER4 architecture component names                 | 12  |

| 2-4  | POWER4 memory and cache organization and per-chip capacity .   | 17  |

| 2-5  | Commonly used adapters, bandwidths, and limits per RIO drawer. | 26  |

| 2-6  | Bandwidth capabilities by I/O stage                            | 26  |

| 3-1  | LPAR memory overhead                                           | 40  |

| 3-2  | Comparison of LPARs to ALPARs                                  | 44  |

| 3-3  | The 32-bit VMM (user) process image                            | 46  |

| 3-4  | Selected application performance and tuning publications       | 60  |

| 3-5  | Important compiler options                                     |     |

| 3-6  | 16 MB message single-plane bandwidths                          | 75  |

| 3-7  | 16 MB message dual-plane bandwidths                            |     |

| 4-1  | Technical large page AIX sort results                          |     |

| 4-2  | Technical large page gabiqsort results                         |     |

| 4-3  | Technical large page (with ALPAR) AIX sort results             |     |

| 4-4  | Technical large page (with ALPAR) gabiqsort results            |     |

| 4-5  | Technical large page (with 16 GB) AIX sort results             |     |

| 4-6  | Technical large page (with 16 GB) gabiqsort results            |     |

| 4-7  | Technical large page (with 4 GB) AIX sort results              |     |

| 4-8  | Technical large page (with 4 GB) gabiqsort results             |     |

| 4-9  | Technical large page (with memory affinity) AIX sort results   |     |

| 4-10 | Technical large page (with memory affinity) gabiqsort results  |     |

| 4-11 | TSM backup with vmtune -L 0                                    |     |

| 4-12 | Test results with 32 technical large pages                     |     |

| 4-13 | Test results with 64 technical large pages                     |     |

| 4-14 | Backup performance for 1 GB with default settings              |     |

| 4-15 | Backup performance for 1 GB with TCPNodelay Yes                |     |

| 4-16 | Backup performance for 1 GB with larger tcpbuffsize            |     |

| 4-17 | Backup performance for 1 GB with ramdisks                      |     |

| 4-18 | Backup performance for 1 GB with tcpwindowsize at 1024         |     |

| 4-19 | IP vs. US test codes                                           |     |

| 4-20 | Results from the parallel (MPI) IP test runs: 4-way/8 GB       |     |

| 4-21 | Results from the parallel (MPI) US test runs: 4-way/8 GB       |     |

| 4-22 | Results from the pcm_04 IP and US test runs: 4-way/8 GB        |     |

| 4-23 | Results from the parallel (MPI) IP test runs: 8-way/16 GB      | 124 |

| 4-24 | Results from the parallel (MPI) US test runs: 8-way/16 GB      | 124 |

| 4-25 | Results from the parallel (MPI) IP test runs new hostfile 125  |

|------|----------------------------------------------------------------|

| 4-26 | Results from the parallel (MPI) US test runs new hostfile 125  |

| 4-27 | The parallel (MPI) IP test runs with shared memory on 126      |

| 4-28 | The parallel (MPI) US test runs with shared memory on 126      |

| 4-29 | Shared memory runs with the IP wrapper script                  |

| 4-30 | Shared memory runs with the US wrapper script                  |

| 4-31 | Comparison of IP vs. US for CHARMm across two 8-way LPARs 140  |

| D-1  | Important software requirements for p690 Clustering 207        |

| D-2  | Coexistence of AIX and PSSP levels                             |

| D-3  | WebSM filesets on the control workstation 209                  |

| D-4  | List with new and enhanced attributes in the frame class 220   |

| D-5  | List with new and enhanced attributes in the Node Class 221    |

| D-6  | List with new and enhanced attributes in the Adapter Class 221 |

| D-7  | Possible node states in SMP mode                               |

| D-8  | Node states in LPAR mode                                       |

| D-9  | Adding a frame                                                 |

| D-10 | Adding nodes231                                                |

| D-11 | Deleting a node                                                |

| D-12 | Adding an Ethernet adapter232                                  |

| D-13 | List of p690-related feature codes                             |

| D-14 | List of useful HMC-related feature codes                       |

## **Notices**

This information was developed for products and services offered in the U.S.A.

IBM may not offer the products, services, or features discussed in this document in other countries. Consult your local IBM representative for information on the products and services currently available in your area. Any reference to an IBM product, program, or service is not intended to state or imply that only that IBM product, program, or service may be used. Any functionally equivalent product, program, or service that does not infringe any IBM intellectual property right may be used instead. However, it is the user's responsibility to evaluate and verify the operation of any non-IBM product, program, or service.

IBM may have patents or pending patent applications covering subject matter described in this document. The furnishing of this document does not give you any license to these patents. You can send license inquiries, in writing, to:

IBM Director of Licensing, IBM Corporation, North Castle Drive Armonk, NY 10504-1785 U.S.A.

The following paragraph does not apply to the United Kingdom or any other country where such provisions are inconsistent with local law: INTERNATIONAL BUSINESS MACHINES CORPORATION PROVIDES THIS PUBLICATION "AS IS" WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. Some states do not allow disclaimer of express or implied warranties in certain transactions, therefore, this statement may not apply to you.

This information could include technical inaccuracies or typographical errors. Changes are periodically made to the information herein; these changes will be incorporated in new editions of the publication. IBM may make improvements and/or changes in the product(s) and/or the program(s) described in this publication at any time without notice.

Any references in this information to non-IBM Web sites are provided for convenience only and do not in any manner serve as an endorsement of those Web sites. The materials at those Web sites are not part of the materials for this IBM product and use of those Web sites is at your own risk.

IBM may use or distribute any of the information you supply in any way it believes appropriate without incurring any obligation to you.

Information concerning non-IBM products was obtained from the suppliers of those products, their published announcements or other publicly available sources. IBM has not tested those products and cannot confirm the accuracy of performance, compatibility or any other claims related to non-IBM products. Questions on the capabilities of non-IBM products should be addressed to the suppliers of those products.

This information contains examples of data and reports used in daily business operations. To illustrate them as completely as possible, the examples include the names of individuals, companies, brands, and products. All of these names are fictitious and any similarity to the names and addresses used by an actual business enterprise is entirely coincidental.

#### COPYRIGHT LICENSE:

This information contains sample application programs in source language, which illustrates programming techniques on various operating platforms. You may copy, modify, and distribute these sample programs in any form without payment to IBM, for the purposes of developing, using, marketing or distributing application programs conforming to the application programming interface for the operating platform for which the sample programs are written. These examples have not been thoroughly tested under all conditions. IBM, therefore, cannot guarantee or imply reliability, serviceability, or function of these programs. You may copy, modify, and distribute these sample programs in any form without payment to IBM for the purposes of developing, using, marketing, or distributing application programs conforming to IBM's application programming interfaces.

#### **Trademarks**

The following terms are trademarks of the International Business Machines Corporation in the United States, other countries, or both:

SPTM **AIX®** Perform™ AIX 5L™ PowerPC® **Tivoli®** e (logo)® @ pSeries™ VisualAge® **ESCON®** Redbooks™ Wave® **IBM®** zSeries™ RS/6000® LoadLeveler®

The following terms are trademarks of International Business Machines Corporation and Lotus Development Corporation in the United States, other countries, or both:

Lotus® Notes® Word Pro®

The following terms are trademarks of other companies:

ActionMedia, LANDesk, MMX, Pentium and ProShare are trademarks of Intel Corporation in the United States, other countries, or both.

Microsoft, Windows, Windows NT, and the Windows logo are trademarks of Microsoft Corporation in the United States, other countries, or both.

Java and all Java-based trademarks and logos are trademarks or registered trademarks of Sun Microsystems, Inc. in the United States, other countries, or both.

C-bus is a trademark of Corollary, Inc. in the United States, other countries, or both.

UNIX is a registered trademark of The Open Group in the United States and other countries.

SET, SET Secure Electronic Transaction, and the SET Logo are trademarks owned by SET Secure Electronic Transaction LLC.

Other company, product, and service names may be trademarks or service marks of others.

## **Preface**

This redbook is based on the firm belief that all good tuning begins and ends with a fundamental understanding of how your system operates within your own environment. There are three main parts to the book. The first two are conceptual. The coverage in the first part includes pSeries 690 internals, such as POWER4, MCMs, memory subsystem, I/O subsystem, and network connectivity (including SP Switch2, SP Switch2 PCI Attachment Adapter, and EtherChannel). Coverage in the second part includes details about performance relevant features, such as affinity logical partitions (ALPARs), scheduling (processor) and memory affinity, technical large page support, and IP vs. US protocol over the new interconnect fabric. The third part details a series of investigations used to see how the new features work and interact. The coverage there includes technical large page, scheduling (processor) and memory affinity, LPAR and ALPAR, Tivoli Storage Manager (TSM), AIX mkramdisk, and IP vs. US. In addition, we have included Configuring p690 in an IBM @server Cluster 1600, REDP0187 as an additional appendix, which will tell you how to configure a pSeries 690 in a Cluster 1600.

#### The team that wrote this redbook

This redbook was produced by a team of specialists from around the world working at the International Technical Support Organization, Poughkeepsie Center.

**Dino Quintero** is a Project Leader at the ITSO Poughkeepsie Center. He currently concentrates on pSeries clustering technologies by writing Redbooks and teaching workshops.

Marc Genty is a Software Engineer in the Supercompute Systems Group at the National Center for Atmospheric Research (NCAR) in Boulder, Colorado, where he supports (among other things) a 318 node Cluster 1600 complex and an early-release pSeries 690 system. He has worked in IT for over 22 years and in the UNIX environments for the last 12 of those years. He is an RS/6000 Certified Advanced Technical Expert (CATE), and he holds a BS degree in Manufacturing from Colorado State University. Marc has also been a contributing author on two other IBM Redbooks, *Exploiting RS/6000 SP Security: Keeping It Safe*, SG24-5521 and *Additional AIX Security Tools on IBM @server pSeries, IBM RS/6000, and SP/Cluster*, SG24-5971.

**Soon-Kwon Ha** is a senior IT specialist in IBM Korea. He has worked at IBM for six years as a RS/6000 and pSeries post-sales support engineer. His areas of expertise include AIX, HACMP, PSSP, system performance tuning, and storage area network (SAN). Currently, Soon-Kwon is working technical support for pSeries and AIX. He has been a contributing author on the IBM Redbook *Configuring the IBM VSS for Performance and Availability*, SG24-5279.

**Tony Pirraglia** is a senior Engineer in the ISV Technical Support group in Poughkeepsie, NY. While currently supporting ISVs in the Life Sciences area, Tony has been involved with Scientific and Technical computing on IBM platforms in one form or another since 1988, when he first joined IBM. He received his Doctorate in Chemical Engineering from Columbia University.

**Gabriel Radu** is a senior IT specialist in IBM Romania. He is an IBM Certified Specialist in AIX, HACMP, and Problem Determination. He has nine years of experience in UNIX systems. His areas of expertise include AIX, HACMP, PSSP, system performance tuning, and Linux. He graduated from the Electronics and Telecommunications Faculty in Bucharest. Currently, Gabriel Radu provides technical support for the RS/6000 and IBM pSeries and AIX.

**Marcelo Ramos** is an Advisory I/T Specialist in IBM Brazil. He is an AIX Certified Specialist and has been working for almost five years in the IBM Integrated Technology Services team, with customer support and services delivery for AIX, HACMP, and PSSP. His areas of expertise include AIX, HACMP, PSSP, ESS, and SAN. He also has some knowledge of Tivoli Storage Manager implementation and support.

Thanks to the following people for their contributions to this project:

International Technical Support Organization, Poughkeepsie Center Al Schwab, Margarita Hunt, David Bennin, Peter Bertolozzi, Michael Schwartz

#### **IBM Boulder**

Tom Farwell and Ishmael Weingarten

#### **IBM Germany**

Stefan Andersson, Christoph Pospiech

#### **IBM Austin**

Raj Panda, Chris Strauss, Steve White, Bruce Hurley

#### **IBM Dallas**

Hari Reddy

#### **IBM Poughkeepsie**

Joan McComb, Jan Ranck-Gustafson, Bernard King-Smith, Frank Johnston,

James Dykman, Hok Chau, Al Dimisko, Xinghong He, Swamy Kandadai, Farid Parpia, Barry Spielberg, Clarisse Taaffe-Hedglin, Jim Wang

#### **IBM Watson**

Bob Walkup and Marge Momberger

#### NCAR, Boulder

George Fuentes, Gene Harano, Bernie O'Lear, Pete Peterson, Al Kellie, Dan Anderson, Pam Gillman, Tom Bettge, Bill Anderson, John Ellis

## Become a published author

Join us for a two- to six-week residency program! Help write an IBM Redbook dealing with specific products or solutions, while getting hands-on experience with leading-edge technologies. You'll team with IBM technical professionals, Business Partners and/or customers.

Your efforts will help increase product acceptance and customer satisfaction. As a bonus, you'll develop a network of contacts in IBM development labs, and increase your productivity and marketability.

Find out more about the residency program, browse the residency index, and apply online at:

ibm.com/redbooks/residencies.html

#### **Comments welcome**

Your comments are important to us!

We want our Redbooks to be as helpful as possible. Send us your comments about this or other Redbooks in one of the following ways:

▶ Use the online **Contact us** review redbook form found at:

ibm.com/redbooks

Send your comments in an Internet note to:

redbook@us.ibm.com

Mail your comments to:

IBM Corporation, International Technical Support Organization Dept. JN9B Mail Station P099 2455 South Road Poughkeepsie, NY 12601-5400

# 1

## Introduction

We begin with a story.

Not long ago, several close friends from the U.S. were vacationing together in Europe. The day was drawing to a close, so they decided to take a room in a small town in the south of France. The cost of the room for the night was \$30.00 U.S. They paid the fee and went up to their room to get settled. Shortly afterwards, the owner of the hotel realized that he had charged them for the single-occupancy rate rather than the lower, multiple-occupancy rate. He owed them a \$5.00 refund. He knew that they were planning to leave early the next morning, so he summoned his son to the front desk and asked him to take the \$5.00 up to the room and explain what had happened. On the way up to the room, the son realized that splitting \$5.00 three ways was far beyond his math skills. So, instead, when he got to the room, he explained the overcharge and gave them each back \$1.00. Now, that means that each of them paid \$9.00 for the room. Three times \$9.00 is \$27.00, plus the \$2.00 that the son pocketed is \$29.00. What happened to the other \$1.00?

Performance and tuning on computers in general and on clusters in particular is much like trying to find the missing \$1.00. You know the answer is right in front of you, and, as soon as you see the problem, you wonder why you were not able to see it all along. The intent of this redbook is to arm you with the additional tools, techniques, information, and references that will help you more quickly find the missing \$1.00.

This redbook is meant to complement rather than replace existing Redbooks and manuals on the subject of performance and tuning. It focuses specifically on how to tune the pSeries 690 in a Cluster 1600. To help you more easily understand where this book fits in the grand scheme of things, Table 1-1 provides an abbreviated list of this and other related IBM books on the subject.

Table 1-1 Other related IBM publications

| Description                                            | Redpaper, redbook, whitepaper, or manual                                                                                                                                                                |

|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| How to tune the p690 in a Cluster 1600.                | Performance and Tuning Considerations for<br>the p690 in a Cluster 1600, SG24-6841<br>(redbook).                                                                                                        |

| How to configure the p690 in a Cluster 1600.           | Configuring p690 in an IBM @server Cluster 1600, REDP0187 (Redpaper). We have also included this redpaper as Appendix D, "Integrating p690 in an IBM eServer Cluster 1600" on page 183 in this redbook. |

| How to tune an RS/6000 SP system.                      | RS/6000 SP System Performance Tuning Update, SG24-5340 (redbook).                                                                                                                                       |

| How to tune an AIX system.                             | AIX Performance Monitoring and Tuning Guide, SC23-2365 (manual).                                                                                                                                        |

| How to tune applications for the POWER4 processor.     | The POWER4 Processor Introduction and Tuning Guide, SG24-7041 (redbook).                                                                                                                                |

| How to monitor and measure the systems in the cluster. | AIX 5L Performance Tools Handbook,<br>SG24-6039 (redbook).                                                                                                                                              |

The what, where, when, why, and how of performance tuning in a clustered environment are well documented in the *RS/6000 SP System Performance Tuning Update*, SG24-5340. What follows is a very brief summary of what we feel are the key points to performance tuning in a clustered environment:

- Know your system, and know your workload.

- Document before and after you make a change.

- Change one thing at a time, and have a backout plan.

- Know how to measure what you are changing.

- When possible, measure with more than one tool.

- Distinguish between systemic versus isolated performance issues.

- For isolated (node) problems, look for bottlenecks in the following order: CPU, memory, disk I/O, and network. For systemic (cluster) problems, look for bottlenecks in the opposite order.

In the chapters that follow, we give you an overview of the hardware components that you can use to build a Cluster 1600 from one or more POWER4 pSeries 690 frames. We cover two types of interconnects: the SP Switch2 with the SP Switch2 PCI Attachment Adapter, and the 10/100/1000 Ethernet. Following the hardware overview, we move on to cover new features that are important to performance, such as logical partitions (LPARs) and affinity logical partitions (ALPARs), scheduling and memory affinity, technical large page support, 32-bit versus 64-bit kernel, aggregate IP over the SP Switch2 with the SP Switch2 PCI Attachment Adapter, and the use of Internet Protocol (IP) versus User Space (US) protocol across the SP Switch2. Finally, we end with a description of and findings from a number of "what if" scenarios that we tested in our laboratory. In the appendices, you will find a summary of the tools that we found useful for measuring, monitoring, poking, and prodding these clustered systems. This is also where we have collected the scripts that were used during our experiments in the laboratory, as well as those that we brought with us from our home sites and thought might be of use to others.

## Hardware overview

This chapter provides the conceptual framework for the remainder of the book. We discuss some of the key components that comprise a Cluster 1600 complex. This is by no means a complete list of every possible configuration, nor is it an in-depth treatise on hardware internals. There are already a number of good IBM manuals, Redbooks, whitepapers, and Redpapers on these subjects. Instead, this chapter focuses on the new components that you can use to construct or integrate into your Cluster 1600 complex. The topics covered are:

- ▶ What is a Cluster 1600?

- ► The pSeries 690 POWER4 building blocks.

- The interconnect fabric.

You may have noticed that there is no mention of external storage systems. There is already a wealth of information available on this subject, so there is no need to duplicate it here. Here are a few references to get you started:

- ► Logical Volume Manager (LVM): AIX Logical Volume Manager, From A to Z: Introduction and Concepts, SG24-5432

- ► Virtual Shared Disk (VSD) and General Parallel File System (GPFS): RS/6000 SP System Performance Tuning Update, SG24-5340

- ▶ Journaled File System 2 (JFS2): AIX 5L Differences Guide, SG24-5765

In Chapter 3, "Features relevant to performance" on page 35, we build on the foundation laid by this one. We go into more detail about the performance

implications and trade-offs that you need to consider when architecting and configuring these components into your cluster. The information presented in this chapter is a prerequisite for all that follows.

#### 2.1 What is a Cluster 1600

So, what is a Cluster 1600 anyway? According to one definition it is:

Cluster 1600 (klus 'ter siks 'teen' hun' drid) noun. 1. A Cluster 1600 is a new cluster name and ID that unifies pSeries cluster offerings, broadens the range of building blocks, increases configuration flexibility, and extends the cluster management domain.

In other words, a Cluster 1600 complex is what used to be called an RS/6000 SP complex, but the name has been changed to emphasize the fact that it now encompasses much more than frames with SP nodes and an occasional SP-attached server. In fact, it is possible to have a Cluster 1600 complex comprised entirely of pSeries nodes. Table 2-1 lists the currently supported node building blocks for the Cluster 1600.

Table 2-1 Cluster 1600 node building blocks

| Model type | Description           | Switch adapters                                                            |

|------------|-----------------------|----------------------------------------------------------------------------|

| 7040-681   | pSeries 690 Model 681 | SP System Attachment Adapter/SP Switch2 PCI Attachment Adapter             |

| 7017-S85   | pSeries 680 Model S85 | SP System<br>Attachment<br>Adapter/SP Switch2<br>PCI Attachment<br>Adapter |

| 7040-671   | pSeries 670 Model 671 | SP System<br>Attachment<br>Adapter/SP Switch2<br>PCI Adapter               |

| 7026-6M1   | pSeries 660 Model 6M1 | SP System Attachment Adapter/SP Switch2 PCI Attachment Adapter             |

| 7026-6H0   | pSeries 660 Model 6H0 | SP System Attachment Adapter/SP Switch2 PCI Attachment Adapter             |

| Model type | Description              | Switch adapters                                                            |

|------------|--------------------------|----------------------------------------------------------------------------|

| 7026-6H1   | pSeries 660 Model 6H1    | SP System<br>Attachment<br>Adapter/SP Switch2<br>PCI Attachment<br>Adapter |

| 9076-2058  | 375MHz SMP High Node     | SP Switch MX2<br>Adapter/SP Switch2<br>Adapter                             |

| 9076-2057  | 375/450MHz SMP Wide Node | SP Switch MX<br>Adapter/SP Switch2<br>MX2 Adapter                          |

| 9076-2056  | 375/450MHz SMP Thin Node | SP Switch MX<br>Adapter/SP Switch2<br>MX2 Adapter                          |

| 9076-2055  |                          | N/A                                                                        |

This redbook focuses exclusively on the performance of pSeries 690 node types. For information on the performance of other node types, see the *RS/6000 SP System Performance Tuning Update*, SG24-5340.

There are now new switch interconnect options available with the Cluster 1600. In addition to the supported SP Switch, there is the SP Switch2, which brings with it the SP Switch2 PCI Attachment Adapter for the pSeries 690 nodes. Table 2-2 lists the raw peak performance numbers for both latency and bandwidth on the two SP switch types.

Table 2-2 Interconnect hardware latency and peak bandwidth

| Nodes in the cluster | Interconnect<br>type | Latency<br>(usec) | Bandwidth<br>(MB/sec)<br>[unidirectional] | Bandwidth<br>(MB/sec)<br>[bidirectional] |

|----------------------|----------------------|-------------------|-------------------------------------------|------------------------------------------|

| Up to 16             |                      | 1.0               |                                           |                                          |

| 17 to 80             | SP Switch2           | 1.5               | 500                                       | 1000                                     |

| 81 to 512            |                      | 2.5               |                                           |                                          |

| Up to 16             |                      | 1.3               |                                           |                                          |

| 17 to 80             | SP Switch            | 1.9               | 150                                       | 300                                      |

| 81 to 512            |                      | 3.3               |                                           |                                          |

For more information on the SP Switch versus SP Switch2 performance numbers, see the RS/6000 SP: SP Switch and SP Switch2 Performance whitepaper at:

http://www.ibm.com/servers/eserver/pseries/hardware/whitepapers/sp\_switch\_perf. html

The pSeries 690 nodes and the new interconnect fabric are covered in the sections that follow.

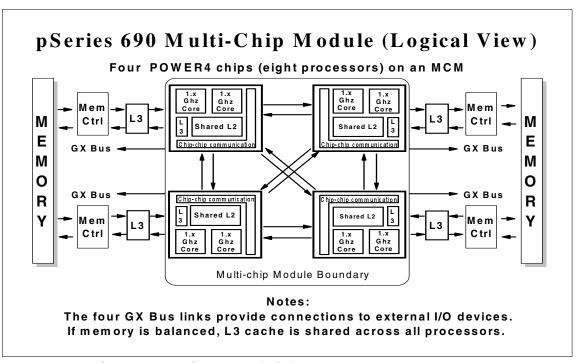

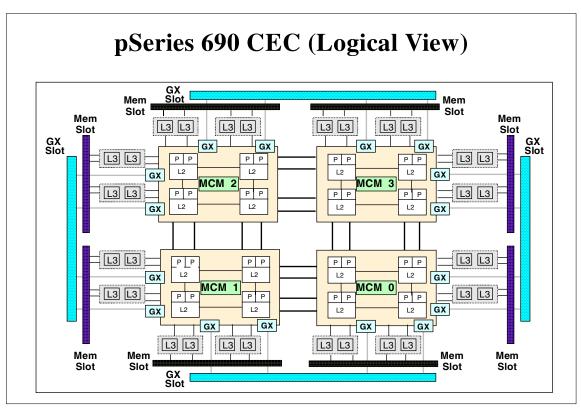

## 2.2 The pSeries 690 POWER4 building blocks

The latest addition to the list of Cluster 1600 node building blocks is the new pSeries 690 POWER4 system. The pSeries 690 is an enterprise class server incorporating the following features:

- ► POWER4 processors (1.1 GHz or 1.3 GHz)

- ► From one to four Multi-Chip Modules (MCMs), each with:

- Either four 2-way or four 1-way (HPC option) POWER4 chips.

- Individual L1 data and instruction caches.

- Shared L2 cache running at processor speed. (Note that the L2 is not shared on models configured with the HPC option.)

- The L3 directory and cache controller.

- The fabric bus controller, providing inter-chip and intra-chip interconnection.

- The GX bus controller, providing connection to external I/O devices.

- Scalable SMP, from 8-way up to 32-way

- Scalable memory, from 8 GB up to 256 GB

- On-chip L1 and L2 cache and off-chip L3 cache

- Support for logical partitioning (LPARs)

- Scalable I/O, from one to eight drawers. Each drawer contains 20 PCI slots and up to 16 disk drives

There are three types of configurations for the pSeries 690:

► The turbo configuration, with eight 1.3 GHz POWER4 processors per MCM and shared L2 cache. It is available as an 8-way (one MCM), a 16-way (two MCMs), a 24-way (three MCMs), or a 32-way (four MCMs) system.

- ► The standard configuration with eight 1.1 GHz POWER4 processors per MCM and shared L2 cache. It is available as an 8-way (one MCM), a 16-way (two MCMs), a 24-way (three MCMs), or a 32-way (four MCMs) system.

- ➤ The High Performance Computing (HPC) configuration with four 1.3 GHz POWER4 processors per Multi-Chip Module (MCM) and dedicated L2 cache. It is available as either an 8-way (two MCMs) or a 16-way (four MCMs) system. This configuration has only four processors per MCM, which effectively doubles the amount of per processor L2 and L3 cache and increases the effective memory bandwidth. This is because the memory subsystem is the same as with the turbo and standard configurations, but the number of processors per chip is half.

Unless otherwise noted, the turbo configuration will be used to illustrate the concepts in this chapter and the next.

In a Cluster 1600 configuration, each pSeries 690 appears as a frame and each LPAR appears as a thin node. There can be from one to 16 LPARs per pSeries 690, but, as we will explain later, there are certain constraints that can put a practical limit on this number to something below 16.

In the discussion that follows, we break the hardware down into:

- ► The processor subsystem

- ► The memory subsystem

- ► The input/output subsystem

Once these have been described, we move on to cover the subject of logical partitions (LPARs). An LPAR is a strange form of ethereal spirit that dwells in the realm between the world of hardware and the world of software. To hardware, LPARs look like software, but to software, LPARs look like hardware. This is a bit of an oversimplification, but as you begin to try to explain this stuff to your coworkers and others, you will perfectly understand the dilemma.

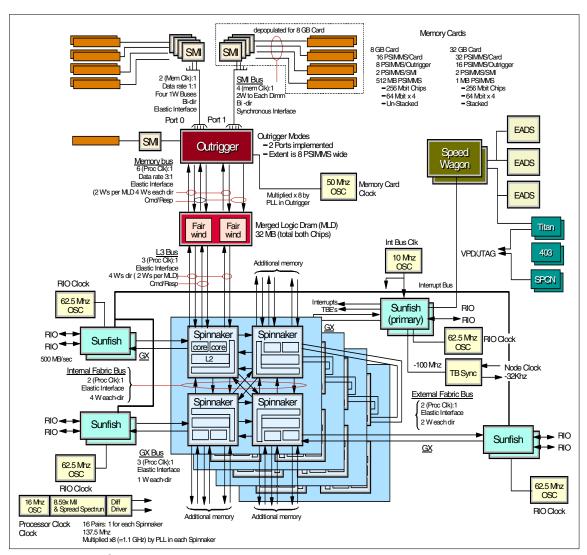

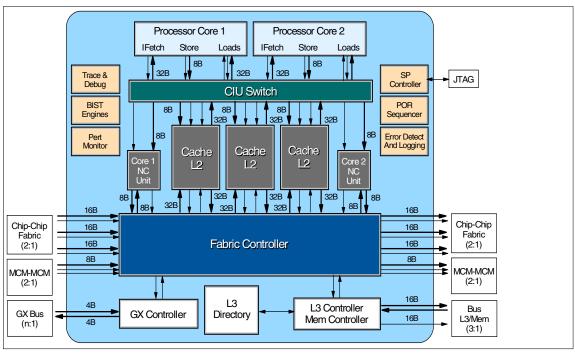

Before we dig into the guts of the pSeries 690, we thought it might be fun to give you the big picture. The heart of the pSeries 690 is contained in a Central Electronics Complex (CEC). This is where the MCMs, memory cards, and connections to the I/O drawers are located. Much of what is shown in Figure 2-1 on page 11 will not be covered in this redbook. Consider this the Rosetta stone for the pSeries 690.

Figure 2-1 The pSeries 690 architecture

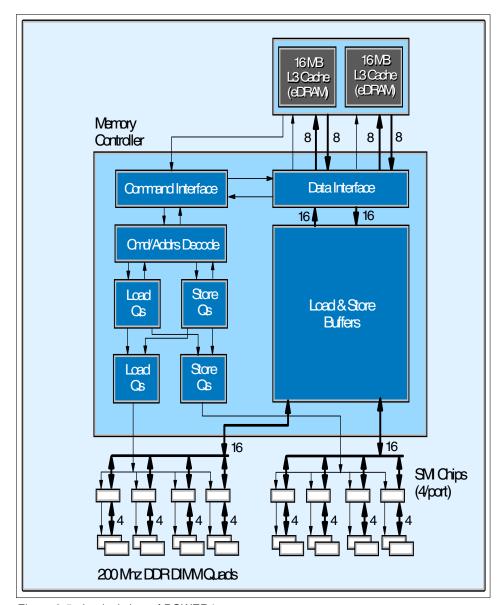

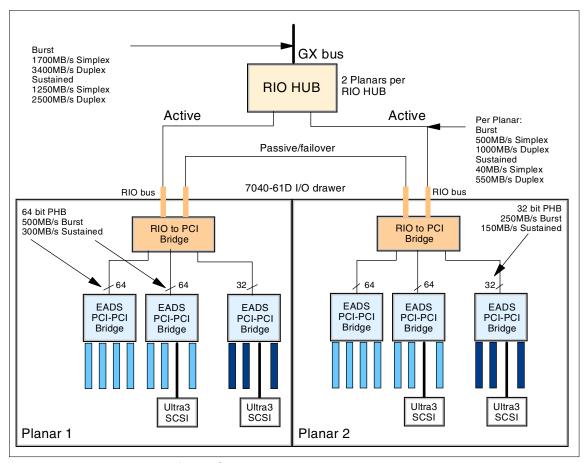

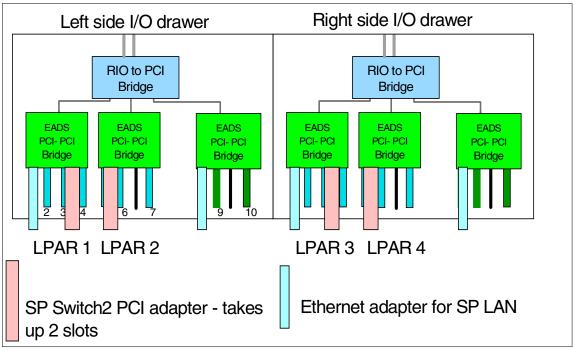

Table 2-3 provides the translation between the diagram component code names and their common external names. Both names are included here because you are likely to run across either name in other publications about the POWER4 architecture.

Table 2-3 Mapping of POWER4 architecture component names

| Diagram component name | Common external name       |  |

|------------------------|----------------------------|--|

| Spinnaker              | POWER4 chip                |  |

| Sunfish                | RIO hub                    |  |

| Fairwind               | L3 cache chip              |  |

| Outrigger              | Memory controller          |  |

| Speed Wagon            | RIO to PCI bridge chip     |  |

| EADS                   | PCI Host Bridge (PHB) chip |  |

If you would like to read more about the low-level internals of the pSeries 690 nodes, we recommend the following two whitepapers:

► The IBM @server pSeries 690 Reliability, Availability, Serviceability (RAS), found at:

http://www.ibm.com/servers/eserver/pseries/hardware/whitepapers/p690\_ras.ht ml

► IBM @server POWER4 System Microarchitecture, found at:

http://www.ibm.com/servers/eserver/pseries/hardware/whitepapers/power4.html

(The pSeries 690 architecture figure is from the first whitepaper listed here.)

### 2.2.1 The processor subsystem