# NIMA POST-PROCESS BANNER TO BE REMOVED AFTER FINAL ACCEPTANCE

## Characterisation of analogue MAPS fabricated in 65 nm technology for the ALICE ITS3

Kunal Gautam<sup>a,b,1,\*</sup>, Ajit Kumar<sup>c</sup>

nm process and study the effects of the modification.

The Analogue Pixel Test Structure (APTS) [4] is a small  $6 \times 6$ pixel matrix with a fast direct analogue readout of the central  $4 \times 4$  pixels, and the Circuit Exploratoire 65 (CE-65) [5] features a  $64 \times 32$  or  $48 \times 32$  pixel matrix with a rolling-shutter

\*Corresponding author

Email address: kunal.gautam@cern.ch (Kunal Gautam )

<sup>1</sup>On behalf of the ALICE Collaboration

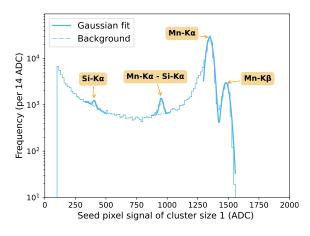

with the <sup>55</sup>Fe radioactive source. The <sup>55</sup>Fe spectrum for events with cluster size of 1 is depicted in Figure 1. A cluster is defined as the set of adjacent pixels within a  $3 \times 3$  matrix centred around the seed pixel, the pixel collecting the highest charge above a threshold. The most prominent Mn-K $_{\alpha}$  peak is used to convert the ADC units to  $e^{-}$ . The linearity of the pixel response was established by fitting all peaks in the spectrum in a high-statistics scan.

Figure 1: <sup>55</sup>Fe spectrum in single-pixel cluster events measured in the central 4 pixels of the APTS.

## 2.2. Detection Efficiency

The test-beam measurements were performed with a telescope using 6 ALPIDE chips [6] as the reference planes and an APTS (Digital Pixel Test Structure) chip as the trigger with the device-under-test being APTS (CE-65).

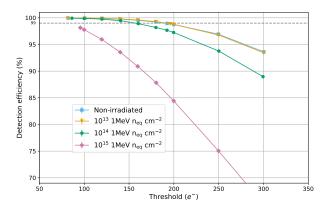

Adding a low dose n-type implant slightly increases the noise RMS of the devices due to the increase in the effective capacitance of the pixels but also significantly improves the range of operation over 99% efficiency. The considerable charge sharing among neighbouring pixels in the standard process causes a significant drop in efficiency with increasing thresholds compared to sensors with process modification. Different pixel geometries, in the form of varying shapes and sizes of the collection electrode and the PWELL enclosure, do not significantly affect the performance, the most notable being the variant with a larger collection electrode, which has a higher noise but is slightly more radiation tolerant.

Figure 2: Efficiency comparison of APTS irradiated to different levels of nonionising radiation. The results correspond to sensors designed in the modified process with gap with the pitch size of 20  $\mu$ m and the bias voltage of 1.2 V. All threshold points are greater than 3×RMS of the noise.

The APTS is performant up to irradiation levels of  $10^{14}$  1 MeV  $n_{eq}$  cm<sup>-2</sup> with the application of the minimal bias voltage

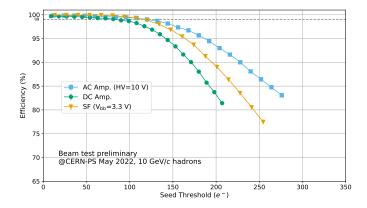

of 1.2 V, as is shown in Figure 2. The effect of depletion on the detection efficiency is depicted in Figure 3. An AC-coupled high voltage provides full depletion of the sensor while disentangled from the readout electronics, gaining high efficiencies even at high thresholds. The depletion depends on the bias voltage for the source-follower configuration, whereas the DC-coupled variant only achieves partial depletion in the absence of biasing, leading to reduced efficiencies at high thresholds.

Figure 3: Effect of depletion on detection efficiency through different in-pixel circuitry in the standard process CE-65.

### 2.3. Spatial Resolution

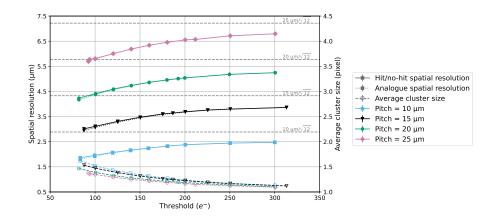

The process modification reduces charge sharing among neighbouring pixels but does not eliminate it. Figure 4 shows that the achieved resolution is better than binary resolution with the average cluster size being greater than one. The APTS reaches a hit/no-hit resolution better than 3  $\mu$ m with a pitch size of 10  $\mu$ m while still operating with over 99% efficiency. The sensors with larger pitch sizes in the modified process with gap show a bigger operational margin with efficiency over 99%.

## 3. Conclusion and Outlook

Additional tests are being pursued to study the effect of collection-electrode placement in the matrix on charge sharing. Further optimisation between detection efficiency and charge sharing is being investigated using pixel designs with AC-coupled high voltage for depletion. The excellent detection efficiency in moderate radiation environments and low spatial resolution make MAPS developed in 65 nm process a viable candidate for the vertex detectors at future lepton colliders, like FCC-ee.

The 65 nm CMOS process has now been validated, and the analogue properties of the sensors have been characterised by consistent results from the small and large matrix prototypes. The performance satisfies the specifications set forth by the AL-ICE ITS3 project.

This project has received funding from the European Union's Horizon 2020 Research and Innovation Programme under Grant Agreements 101004761 (AIDAinnova) and 101057511 (EURO-LABS).

Figure 4: Hit/no-hit resolution (solid lines), analogue resolution (dotted lines), and average cluster size (dashed lines) for several pitch sizes in modified-with-gap process APTS at the bias voltage of 1.2 V.

### References

- The ALICE collaboration, Technical Design report for the ALICE Inner Tracking System 3 – ITS3; A bent wafer-scale monolithic pixel detector, Technical Report, CERN, Geneva, 2024. URL: https://cds.cern.ch/ record/2890181.

- [2] W. Snoeys, et al., A process modification for CMOS monolithic active pixel sensors for enhanced depletion, timing performance and radiation tolerance, Nucl. Instr. Meth. Phys. Res. A 871 (2017) 90-96. URL: https://www.sciencedirect.com/science/article/ pii/S016890021730791X. doi:https://doi.org/10.1016/j.nima. 2017.07.046.

- [3] M. Munker, et al., Simulations of CMOS pixel sensors with a small collection electrode, improved for a faster charge collection and increased radiation tolerance, Journal of Instrumentation 14 (2019) C05013. URL: https://dx.doi.org/10.1088/1748-0221/14/05/C05013. doi:10.1088/1748-0221/14/05/C05013. arXiv:1903.10190.

- [4] G. A. Rinella, et al., Characterisation of analogue monolithic active pixel sensor test structures implemented in a 65 nm cmos imaging process, 2024. arXiv:2403.08952.

- [5] S. Bugiel, et al., Charge sensing properties of monolithic CMOS pixel sensors fabricated in a 65 nm technology, Nucl. Instr. Meth. Phys. Res. A 1040 (2022) 167213. URL: https://www. sciencedirect.com/science/article/pii/S016890022200568X. doi:https://doi.org/10.1016/j.nima.2022.167213.

- [6] G. Aglieri Rinella, et al., The ALPIDE pixel sensor chip for the upgrade of the ALICE Inner Tracking System, Nucl. Instr. Meth. Phys. Res. A 845 (2017) 583-587. URL: https://www. sciencedirect.com/science/article/pii/S0168900216303825. doi:https://doi.org/10.1016/j.nima.2016.05.016.